# F.Y.B.SC.(IT) SEMESTER - I (CBCS)

# **DIGITAL ELECTRONICS**

**SUBJECT CODE: USIT102**

#### © UNIVERSITY OF MUMBAI

#### Prof. Suhas Pednekar

Vice Chancellor University of Mumbai, Mumbai.

Prof. Ravindra D. Kulkarni

Pro Vice-Chancellor, University of Mumbai. Prof. Prakash Mahanwar

Director

IDOL, University of Mumbai.

Programe Co-ordinator : Mandar L. Bhanushe

Head, Faculty of Science and Technology, IDOL, University of Mumbai – 400098.

Course Co-ordinator : Gouri S. Sawant

Assistant Professor, B.Sc. IT, IDOL, University of Mumbai-400098.

Course Writers : Ankush Kudale

Assistant Professor,

Sinhgad Institute of Management, Vadgaon (Bk), Pune

: Sabir Moin. M. Shaikh

Assistant Professor

Vidyalankar School of Information Technology

: Dr. Sunil Khilari

Asst Professor

Sinhgad Institute of Management, Pune.

: Umesh Koyande

Assistant Professor

Vidyalankar School of Information Technology

: Dr. Milind S. Godase

Professor,

Sinhgad Institute of Management, Vadgaon (Bk), Pune

#### June 2021, Print I

Published by : Director

Institute of Distance and Open Learning,

University of Mumbai,

DTP Composed : Varda Offset and Typesetters

Andheri (W), Mumbai - 400 053.

Printed by

# **CONTENTS**

| Chapter I  | No. Title                                                          | Page No |

|------------|--------------------------------------------------------------------|---------|

|            | Unit I                                                             |         |

| Chapter 1  | Number System                                                      | 01      |

| Chapter 2  | Binary Arithmetic                                                  | 26      |

|            | Unit II                                                            |         |

| Chapter 3  | Logic Gates                                                        | 58      |

| Chapter 4  | Sop And Pos Representation of Logical Expressions And Karnaugh Map | 69      |

|            | Unit III                                                           |         |

| -          | Combinational Logic Circuits                                       |         |

| Chapter 6  | Arithmetic Circuits                                                | 114     |

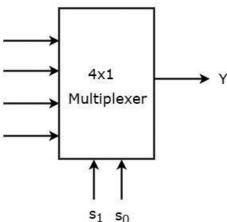

| Chapter 7  | Multiplexer                                                        | 127     |

|            | Unit IV                                                            |         |

| Chapter 8  | Multiplexer And Demultiplexer                                      | 133     |

| Chapter 9  | Flip-Flops                                                         | 141     |

|            | Unit V                                                             |         |

| Chapter 10 | Counters                                                           | 159     |

| Chapter 11 | Registers                                                          | 201     |

\*\*\*\*

# Syllabus

| B. Sc (Information | on Technology)           | Semester | - I           |

|--------------------|--------------------------|----------|---------------|

| Course Name: D     | Digital Electronics      | Course ( | Code: USIT102 |

| Periods per week   | (1 Period is 50 minutes) | 5        |               |

| Credits            |                          | 2        |               |

|                    |                          | Hours    | Marks         |

| Evaluation         | Theory                   | 21/2     | 75            |

| System             | Examination              | -        | 25            |

| Unit | Details                                                                            | Lectures |

|------|------------------------------------------------------------------------------------|----------|

| I    | Number System:                                                                     | 12       |

| •    | Analog System, digital system, numbering                                           | 12       |

|      | system, binary number system, octal number                                         |          |

|      | system, hexadecimal number system,                                                 |          |

|      | conversion from one number system to                                               |          |

|      | another, floating point numbers, weighted                                          |          |

|      | codes binary coded decimal, non-weighted                                           |          |

|      | codes Excess – 3 code, Gray code,                                                  |          |

|      | Alphanumeric codes – ASCII Code, EBCDIC,                                           |          |

|      | ISCII Code, Hollerith Code, Morse Code,                                            |          |

|      | Teletypewriter (TTY), Error detection and                                          |          |

|      | correction, Universal Product Code, Code                                           |          |

|      | conversion.                                                                        |          |

|      | Binary Arithmetic:                                                                 |          |

|      | Binary addition, Binary subtraction, Negative                                      |          |

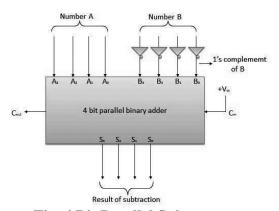

|      | number representation, Subtraction using 1's complement and 2's complement, Binary |          |

|      | multiplication and division, Arithmetic in octal                                   |          |

|      | number system, Arithmetic in hexadecimal                                           |          |

|      | number system, BCD and Excess – 3                                                  |          |

|      | arithmetic.                                                                        |          |

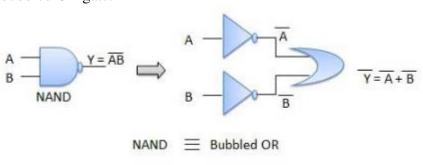

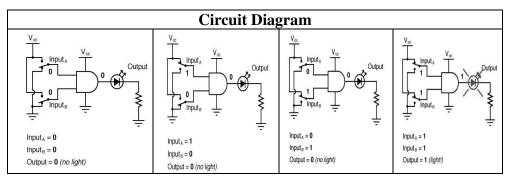

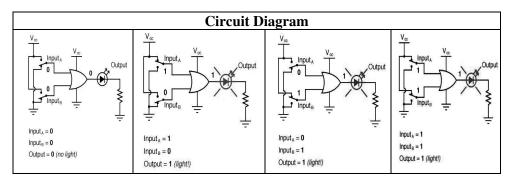

| II   | <b>Boolean Algebra and Logic Gates:</b>                                            | 12       |

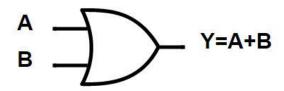

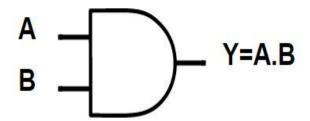

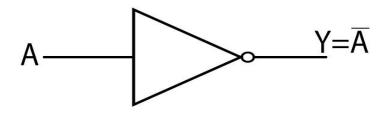

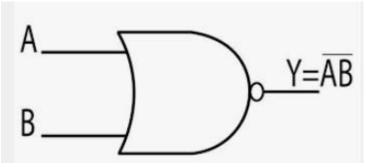

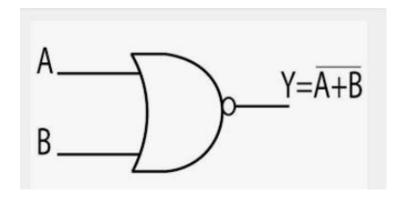

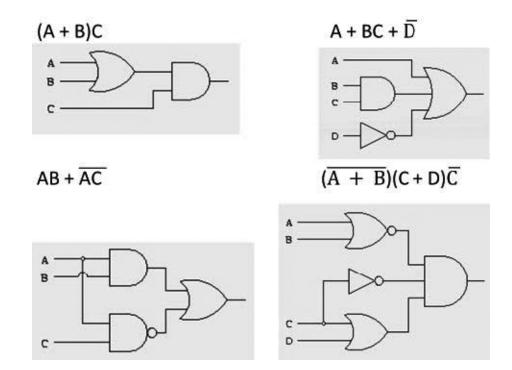

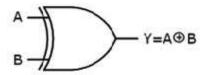

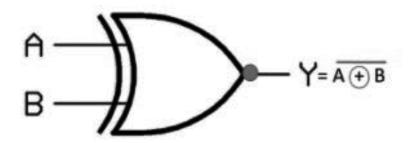

|      | Introduction, Logic (AND OR NOT), Boolean                                          |          |

|      | theorems, Boolean Laws, De Morgan's                                                |          |

|      | Theorem, Perfect Induction, Reduction of                                           |          |

|      | Logic expression using Boolean Algebra,                                            |          |

|      | Deriving Boolean expression from given                                             |          |

|      | circuit, exclusive OR and Exclusive NOR                                            |          |

|      | gates, Universal Logic gates, Implementation                                       |          |

|      | of other gates using universal gates, Input                                        |          |

|      | bubbled logic, Assertion level.                                                    |          |

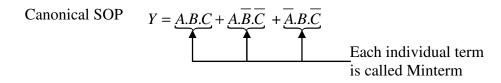

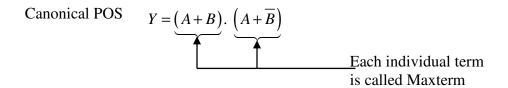

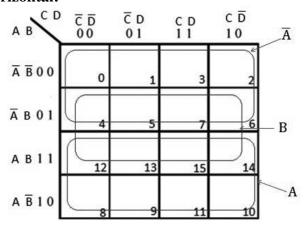

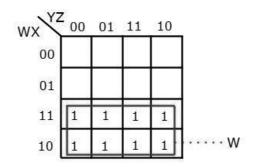

|      | Minterm, Maxterm and Karnaugh Maps:                                                |          |

|      | Introduction, minterms and sum of minterm                                          |          |

|      | form, maxterm and Product of maxterm form,                                         |          |

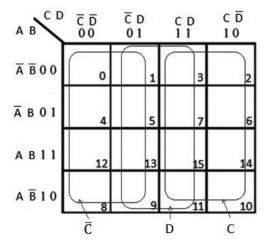

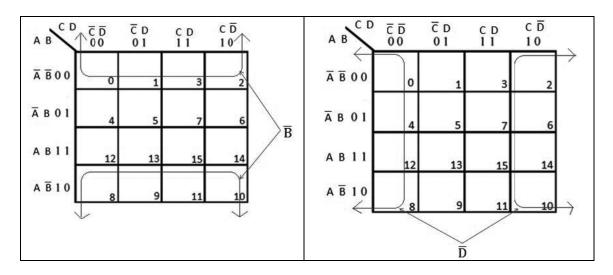

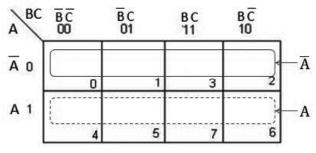

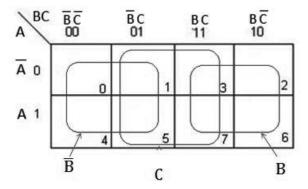

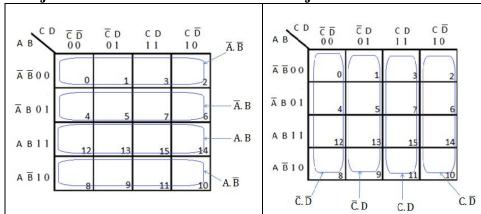

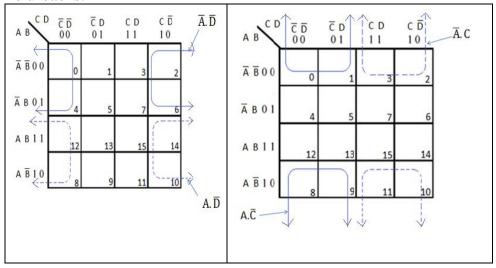

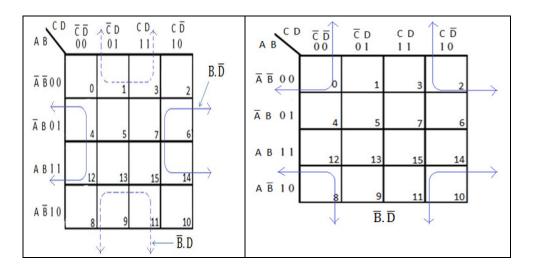

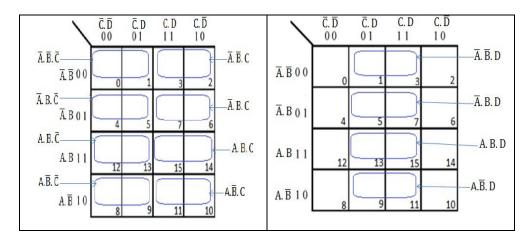

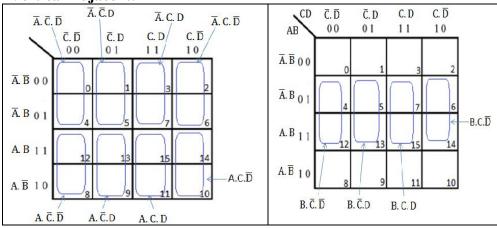

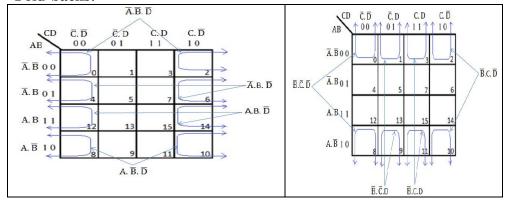

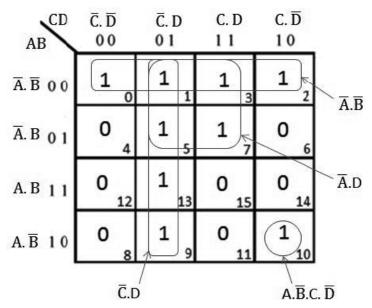

|      | Reduction technique using Karnaugh maps – 2/3/4/5/6 variable K-maps, Grouping of   |          |

|      | variables in K-maps, K-maps for product of                                         |          |

|      | sum form, minimize Boolean expression using                                        |          |

|      | sam form, minimize boolean expression using                                        |          |

|              | K-map and obtain K-map from Boolean                                                |    |

|--------------|------------------------------------------------------------------------------------|----|

|              | expression, Quine Mc Cluskey Method.                                               |    |

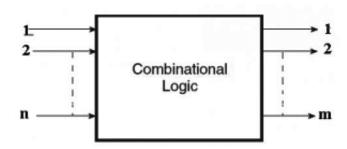

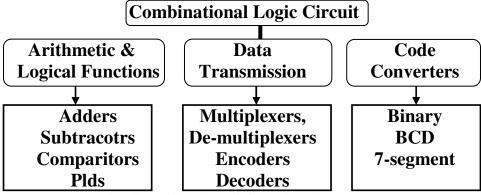

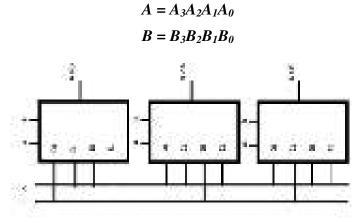

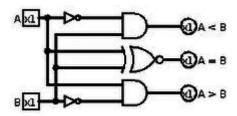

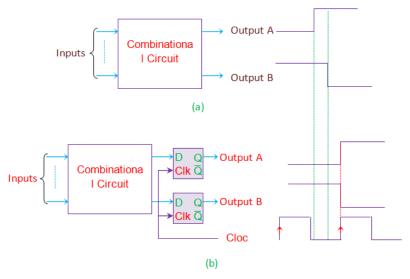

| III          | Combinational Logic Circuits:                                                      | 12 |

| 111          | Introduction, Multi-input, multi-output                                            | 12 |

|              | Combinational circuits, Code converters design                                     |    |

|              | and implementations                                                                |    |

|              | Arithmetic Circuits:                                                               |    |

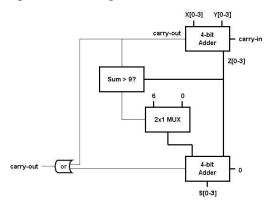

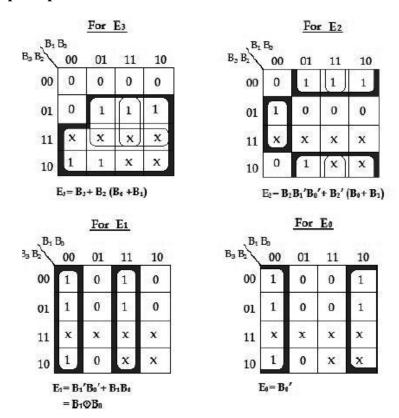

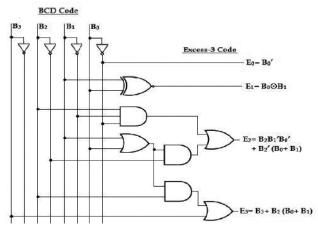

|              | Introduction, Adder, BCD Adder, Excess – 3                                         |    |

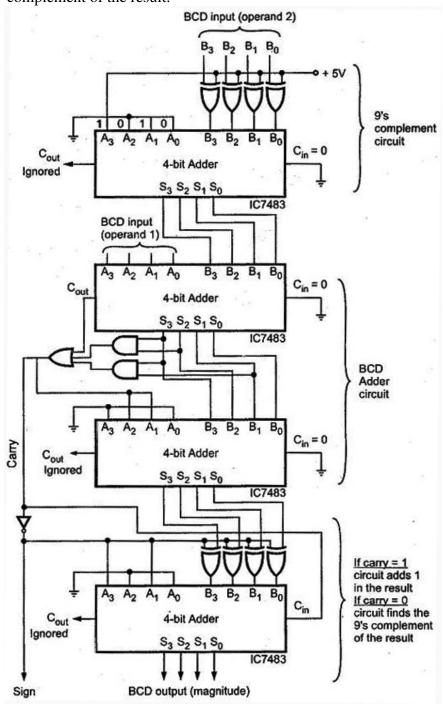

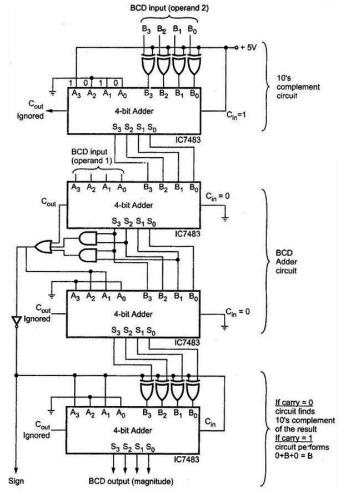

|              | Adder, Binary Subtractors, BCD Subtractor,                                         |    |

|              | Multiplier, Comparator.                                                            |    |

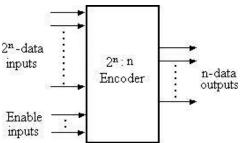

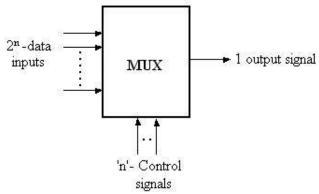

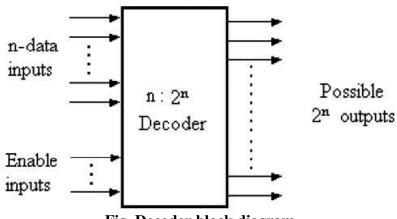

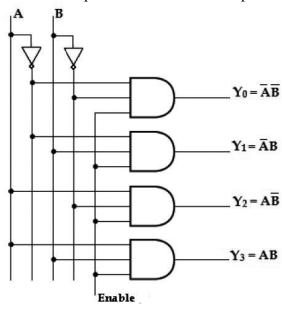

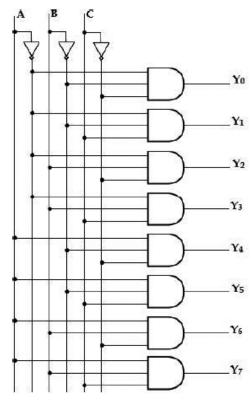

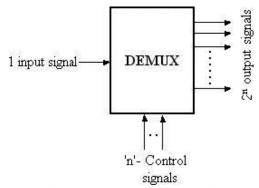

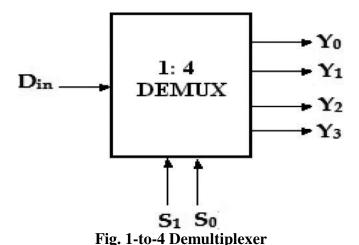

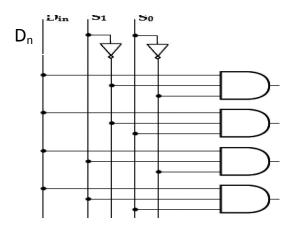

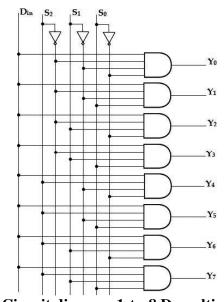

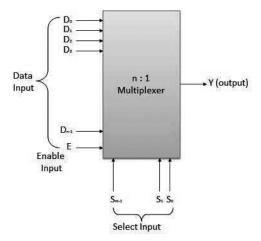

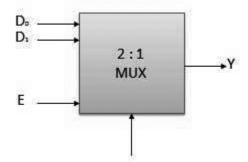

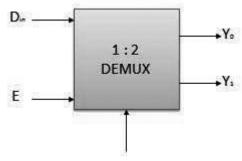

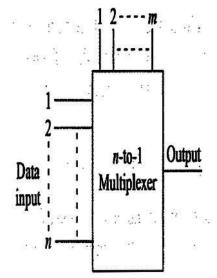

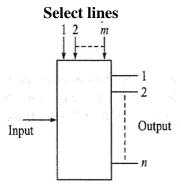

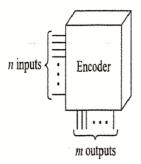

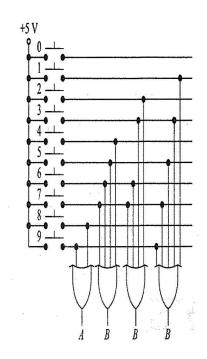

| IV           | Multiplexer, Demultiplexer, ALU, Encoder                                           | 12 |

|              | and Decoder:                                                                       |    |

|              | Introduction, Multiplexer, Demultiplexer,                                          |    |

|              | Decoder, ALU, Encoders.                                                            |    |

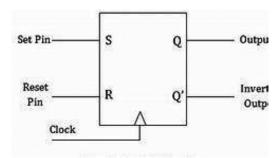

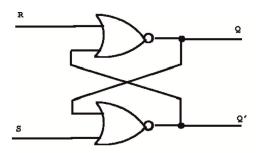

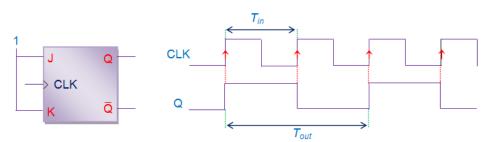

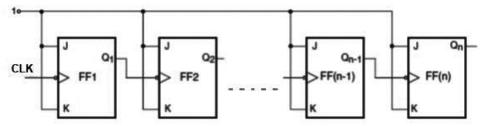

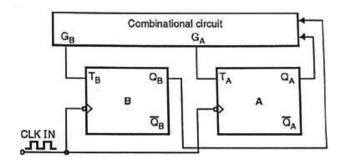

|              | Sequential Circuits: Flip-Flop:                                                    |    |

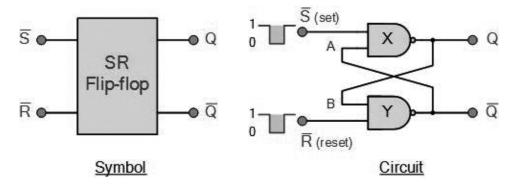

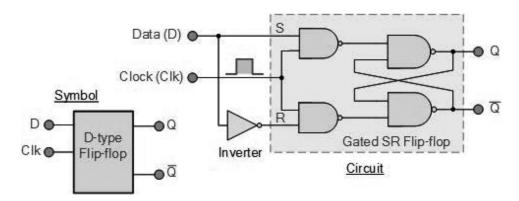

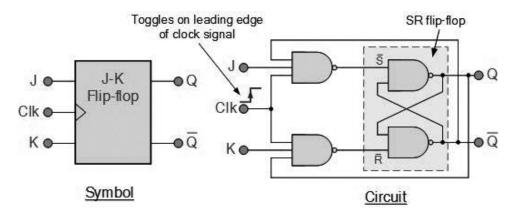

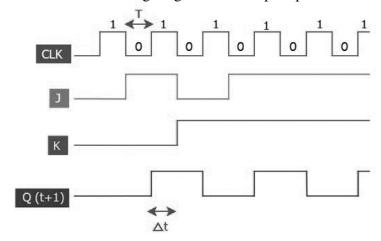

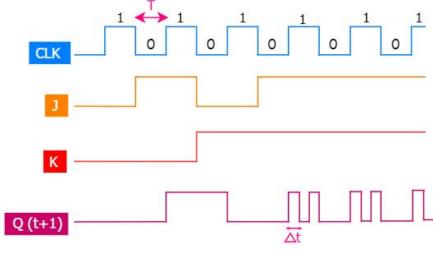

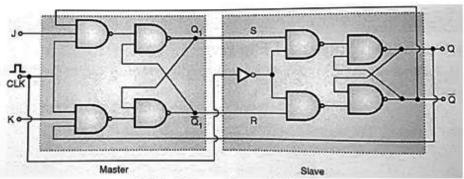

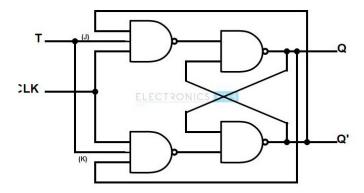

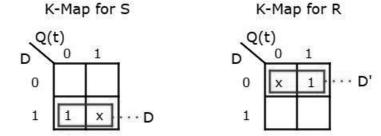

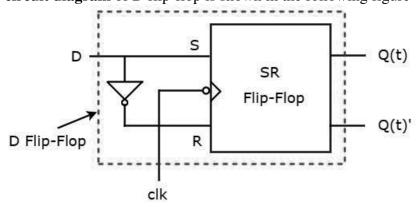

|              | Introduction, Terminologies used, S-R flip-                                        |    |

|              | flop, D flip-fop, JK flipflop, Race-around                                         |    |

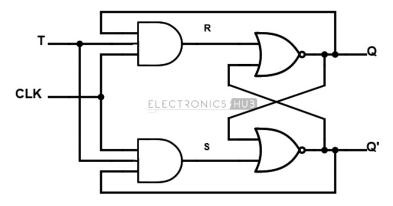

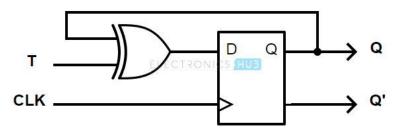

|              | condition, Master – slave JK flip-flop, T flip-                                    |    |

|              | flop, conversion from one type of flip-flop to                                     |    |

| **           | another, Application of flipflops.                                                 | 40 |

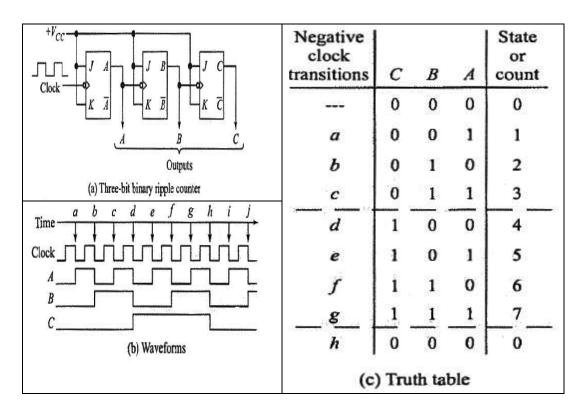

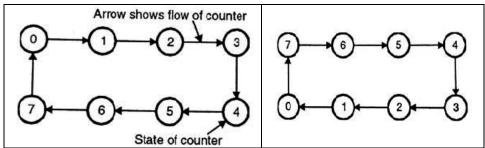

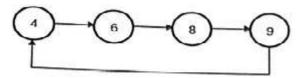

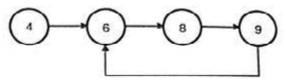

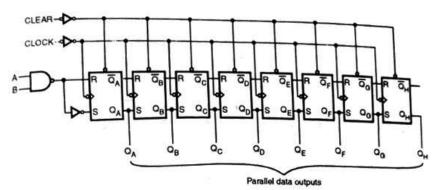

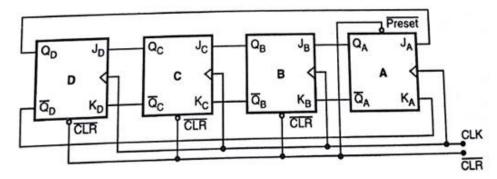

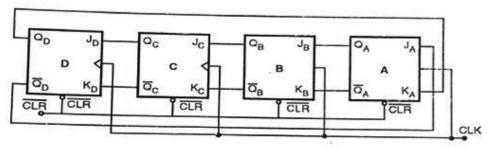

| $\mathbf{V}$ | Counters:                                                                          | 12 |

|              | Introduction, Asynchronous counter, Terms                                          |    |

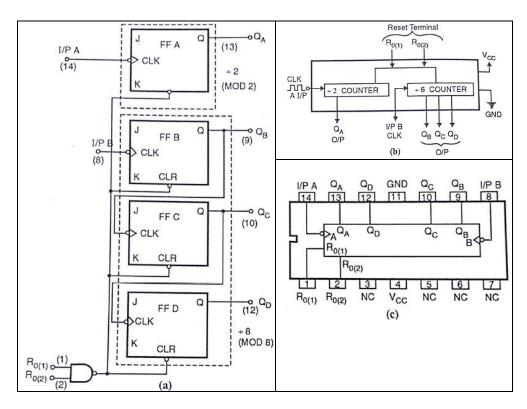

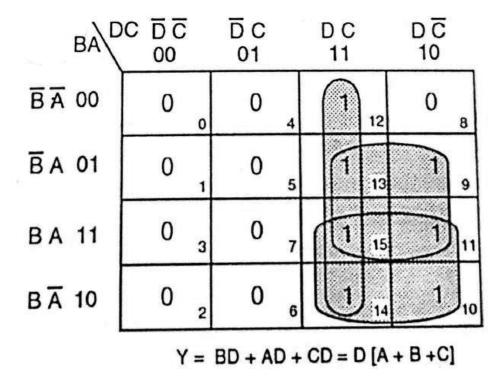

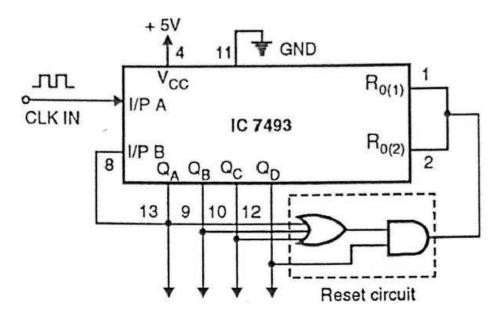

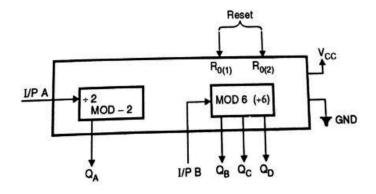

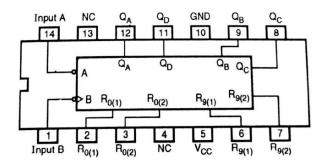

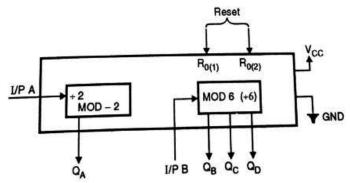

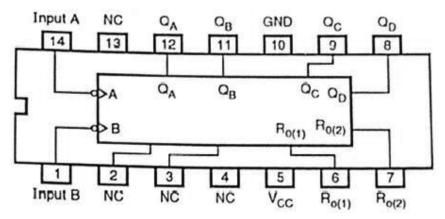

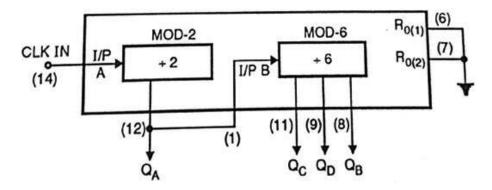

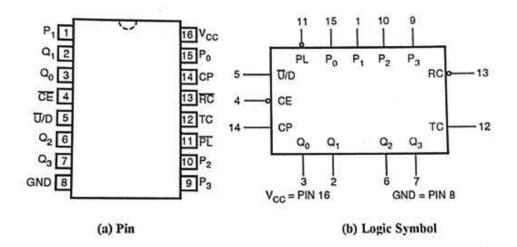

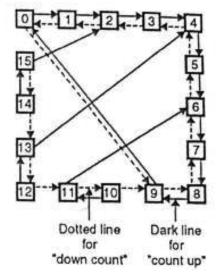

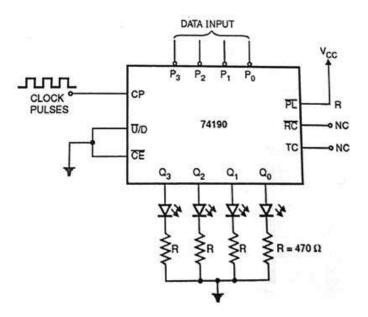

|              | related to counters, IC 7493 (4-bit binary                                         |    |

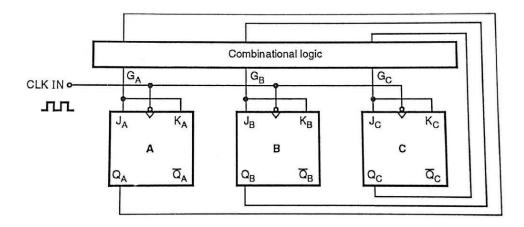

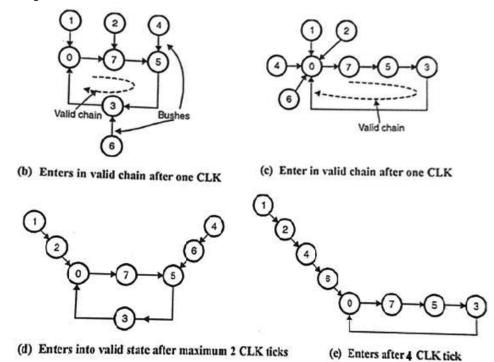

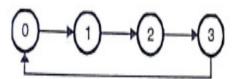

|              | counter), Synchronous counter, Bushing, Type T Design, Type JK Design, Presettable |    |

|              | counter, IC 7490, IC 7492, Synchronous                                             |    |

|              | counter ICs, Analysis of counter circuits.                                         |    |

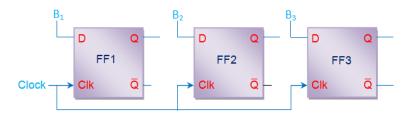

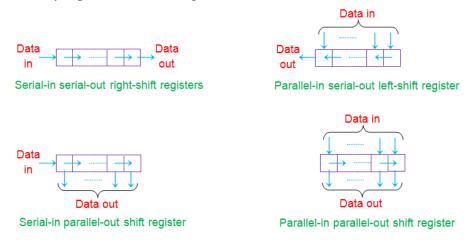

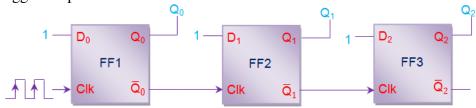

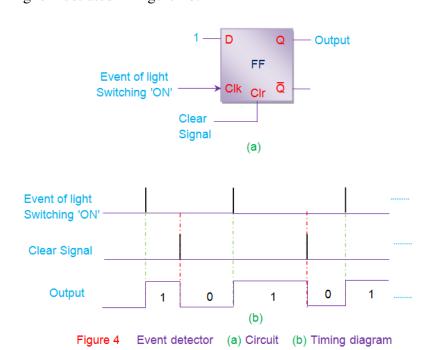

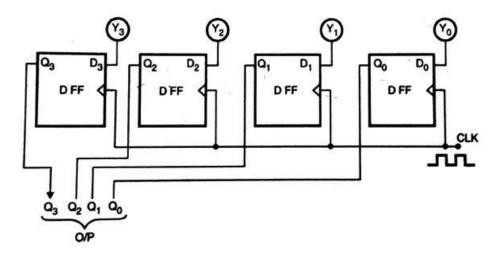

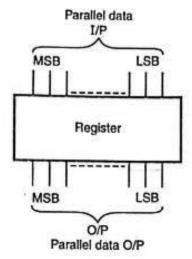

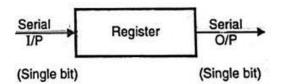

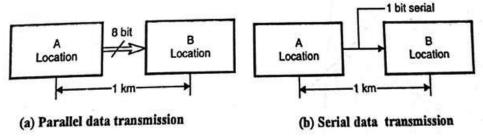

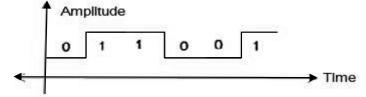

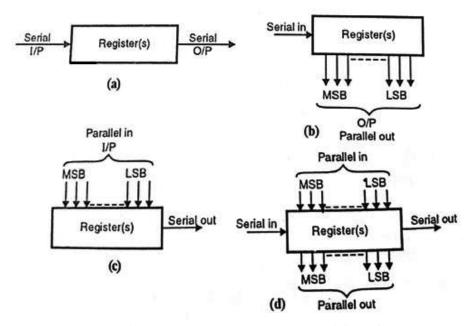

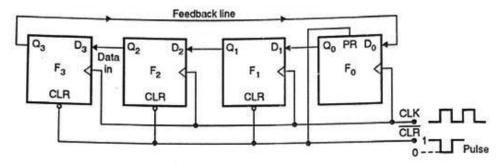

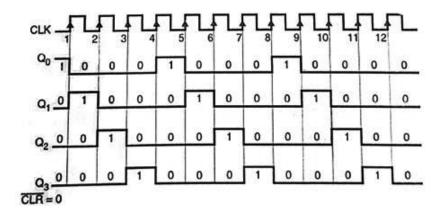

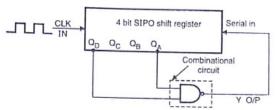

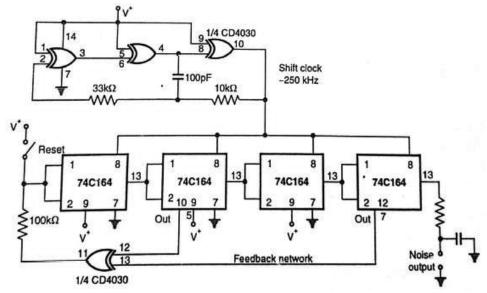

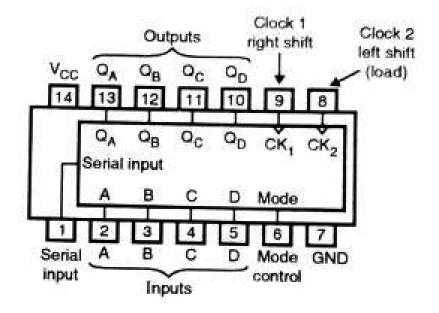

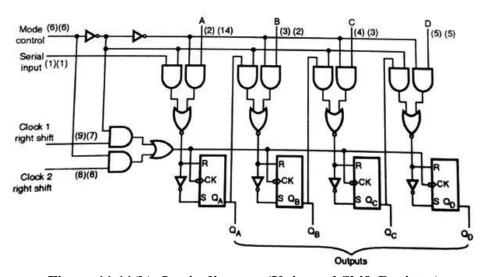

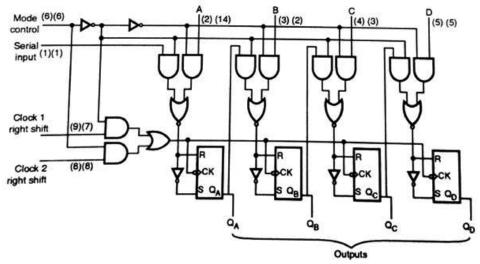

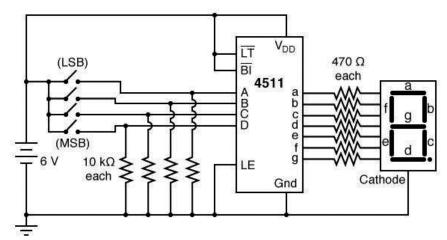

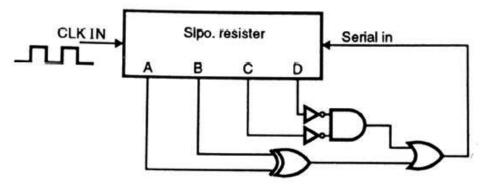

|              | Shift Register:                                                                    |    |

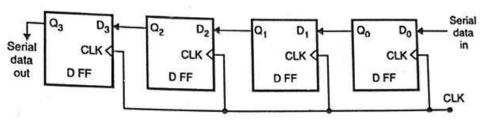

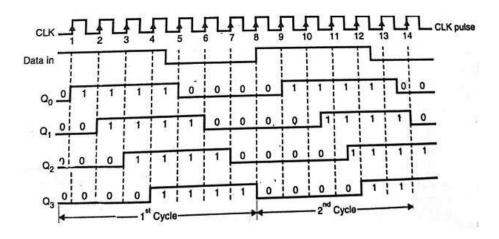

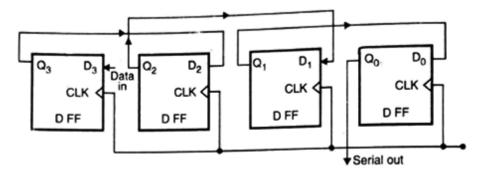

|              | Introduction, parallel and shift registers, serial                                 |    |

|              | shifting, serial—in serial—out, serial—in parallel—                                |    |

|              | out , parallel—in parallel—out, Ring counter,                                      |    |

|              | Johnson counter, Applications of shift                                             |    |

|              | registers, Pseudo-random binary sequence                                           |    |

|              | generator, IC7495, Seven Segment displays,                                         |    |

|              | analysis of shift counters.                                                        |    |

| Book       | Books and References:                |               |                     |                 |      |  |  |

|------------|--------------------------------------|---------------|---------------------|-----------------|------|--|--|

| Sr.<br>No. | Title                                | Author/s      | Publisher           | Editi<br>on     | Year |  |  |

| 1.         | Digital Electronics and Logic Design | N. G. Palan   | Technova            |                 |      |  |  |

| 2.         | Make<br>Electronics                  | Charles Platt | O'Reilly            | 1 <sup>st</sup> | 2010 |  |  |

| 3.         | Modern<br>Digital<br>Electronics     | R. P. Jain    | Tata<br>McGraw Hill | 3 <sup>rd</sup> |      |  |  |

| 4.         | Digital                              | Malvino and   | Tata                |                 |      |  |  |

|    | Principles    | Leach         | McGraw |     |      |

|----|---------------|---------------|--------|-----|------|

|    | and           |               | Hill   |     |      |

|    | Applications  |               |        |     |      |

| 5. | Digital       | Anil K. Maini | Wiley  | 1st | 2007 |

|    | Electronics:  |               |        |     |      |

|    | Principles,   |               |        |     |      |

|    | Devices and   |               |        |     |      |

|    | Applications, |               |        |     |      |

| B. Sc (Information 7  | Semest                       | er – I      |    |  |

|-----------------------|------------------------------|-------------|----|--|

| Course Name: Digita   | Course                       | Course      |    |  |

|                       | Code:U                       | JSIT1P2     |    |  |

| Periods per week (1 F | Period is 50 minutes)        | 5           |    |  |

| Credits               | 2                            |             |    |  |

|                       | Hours                        | Theory      |    |  |

|                       | Marks                        | Examination |    |  |

| Explustion Cystem     | Internal Examination         | 21/2        | 75 |  |

| Evaluation System     | <b>Practical Examination</b> | -           | 25 |  |

|           | List of Practical: (Can be done in any imperative language)      |

|-----------|------------------------------------------------------------------|

| 1         | Study of Logic gates and their ICs and universal gates:          |

| a.        | Study of AND, OR, NOT, XOR, XNOR, NAND and NOR gates             |

| b.        | IC 7400, 7402, 7404, 7408, 7432, 7486, 74266                     |

| c.        | Implement AND, OR, NOT, XOR, XNOR using NAND gates.              |

| d.        | Implement AND, OR, NOT, XOR, XNOR using NOR gates.               |

|           |                                                                  |

| 2.        | Implement the given Boolean expressions using minimum            |

|           | number of gates.                                                 |

| a.        | Verifying De Morgan's laws.                                      |

| b.        | Implement other given expressions using minimum number of gates. |

| c.        | Implement other given expressions using minimum number of ICs.   |

|           |                                                                  |

| <b>3.</b> | Implement combinational circuits.                                |

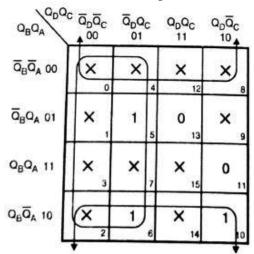

| a.        | Design and implement combinational circuit based on the problem  |

|           | given and minimizing using K-maps.                               |

|           |                                                                  |

| 4.        | Implement code converters.                                       |

| a.        | Design and implement Binary – to – Gray code converter.          |

| b.        | Design and implement Gray – to – Binary code converter.          |

| c.        | Design and implement Binary – to – BCD code converter            |

| d.        | Design and implement Binary – to – XS-3 code converter           |

|           |                                                                  |

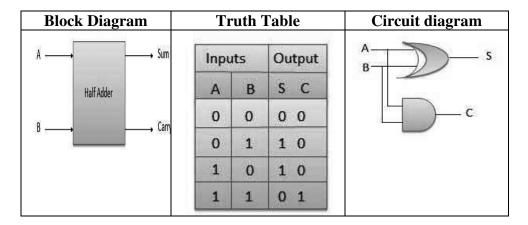

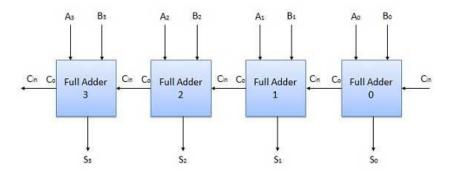

| 5.        | Implement Adder and Subtractor Arithmetic circuits.              |

| a.        | Design and implement Half adder and Full adder.                  |

| b.        | Design and implement BCD adder.                                  |

| c.        | Design and implement XS – 3 adder.                               |

| d.        | Design and implement binary subtractor.                          |

| e.        | Design and implement BCD subtractor.                             |

| f.  | Design and implement XS – 3 subtractor.                                                                                                 |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 6.  | Implement A with motio civavits                                                                                                         |  |  |

|     | Implement Arithmetic circuits.                                                                                                          |  |  |

| a.  | Design and implement a 2-bit by 2-bit multiplier.                                                                                       |  |  |

| b.  | Design and implement a 2-bit comparator.                                                                                                |  |  |

| 7.  | Implement Encode and Decoder and Multiplexer and Demultiplexers.                                                                        |  |  |

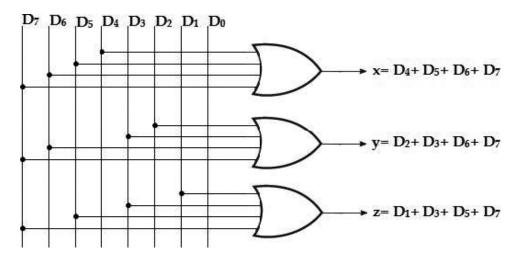

| a.  | Design and implement 8:3 encoder.                                                                                                       |  |  |

| b.  | Design and implement 3:8 decoder.                                                                                                       |  |  |

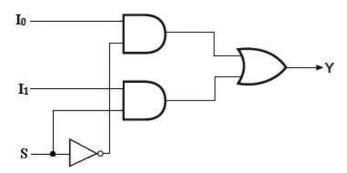

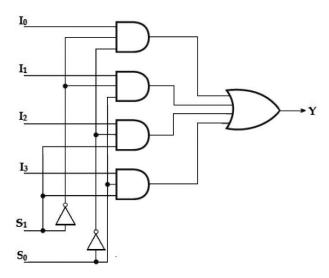

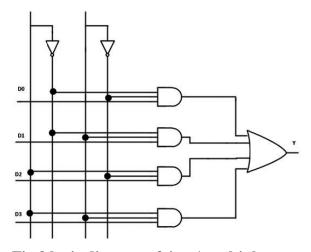

| C.  | Design and implement 4:1 multiplexer.                                                                                                   |  |  |

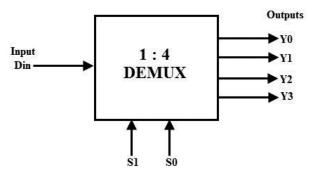

| d.  | Design and implement 1:4 demultiplexer. Study of IC 74139                                                                               |  |  |

| e.  | Implement the given expression using IC 74151 8:1 multiplexer.                                                                          |  |  |

| f.  | Implement the given expression using IC 74138 3:8 decoder.                                                                              |  |  |

| 8.  | Study of flip-flops and counters.                                                                                                       |  |  |

| a.  | Study of IC 7473.                                                                                                                       |  |  |

| b.  | Study of IC 7474.                                                                                                                       |  |  |

| c.  | Study of IC 7476.                                                                                                                       |  |  |

| d.  | Conversion of Flip-flops.                                                                                                               |  |  |

| e.  | Design of 3-bit synchronous counter using 7473 and required gates.                                                                      |  |  |

| f.  | Design of 3-bit ripple counter using IC 7473.                                                                                           |  |  |

| 9.  | Study of counter ICs and designing Mod-N counters.                                                                                      |  |  |

| a.  | Study of IC 7490, 7492, 7493 and designing mod-n counters using these.                                                                  |  |  |

| b.  | Designing mod-n counters using IC 7473 and 7400 (NAND gates)                                                                            |  |  |

| 10. | Design of shift registers and shift register counters.                                                                                  |  |  |

|     | Design serial – in serial – out, serial – in parallel – out, parallel –                                                                 |  |  |

| a.  | in serial – out, parallel – out, serial – in parallel – out, parallel – parallel – out and bidirectional shift registers using IC 7474. |  |  |

| b.  | Study of ID 7495.                                                                                                                       |  |  |

| c.  | Implementation of digits using seven segment displays.                                                                                  |  |  |

| Books      | Books and References:                     |                         |                    |         |      |  |  |

|------------|-------------------------------------------|-------------------------|--------------------|---------|------|--|--|

| Sr.<br>No. | Title                                     | Author/s                | Publisher          | Edition | Year |  |  |

| 1.         | Digital Electronics and Logic Design      | N. G.<br>Palan          | Technova           |         |      |  |  |

| 2.         | Digital<br>Principles and<br>Applications | Malvino<br>and<br>Leach | Tata McGraw<br>Hil |         |      |  |  |

## **NUMBER SYSTEM**

#### **Unit Structure**

- 1.0 Objectives

- 1.1 Introduction

- 1.2 Analog system, digital system

- 1.3 Numbering system

- 1.4 Conversion from one number system to another

- 1.5 Floating point numbers

- 1.6 Weighted codes binary coded decimal

- 1.7 Non-weighted codes Excess 3 code

- 1.8 Gray code

- 1.9 Alphanumeric codes

- 1.10 Error detection and correction

- 1.11 Universal Product Code

- 1.12 Code conversion

## 1.0 OBJECTIVES

This chapter would make you understand the following concepts

- What is difference between analog and digital system?

- Different numbering system.

- Conversion from one number system to another

- Floating point numbers

- Weighted codes binary coded decimal

- Non-weighted codes Excess 3 code

- Gray code and Alphanumeric codes

- Error detection and correction

- Universal Product Code and Code conversion

## 1.1 INTRODUCTION

The study of number systems is important from the viewpoint of understanding how data are represented before they can be processed by any digital system including a digital computer. In this chapter we will discuss different number systems commonly used to represent data such as the binary, octal and hexadecimal number systems.

## 1.2 ANALOG SYSTEM, DIGITAL SYSTEM

Digital as well as Analog System, both are used to transmit signals from one place to another like audio/video. Digital system uses binary format as 0 and 1 whereas analog system uses electronic pulses with varying magnitude to send data.

#### 1.2.1 Analog system:

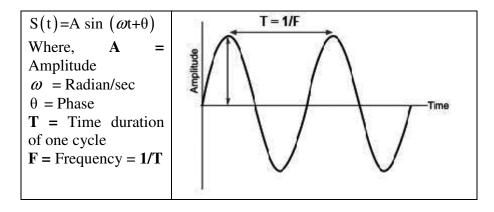

A signal is defined as any physical quantity that varies with time, space, or any other independent variable or variables. Mathematically signal can be function of one or more independent variables, for example,

$$S_1(t) = 10 t$$

$S_2(t) = 10 t^2$

Most of the signals find in science and engineering are analog in nature i.e. the signals are functions of a continuous variable, such as time or space, and usually take on values in continuous range. The most common example of analog signal is sinusoidal waveform as shown Fig. 1.2.1

The expression for the signal can be written as S(t)=A sin  $(\omega t + \theta)$

To measure an analog signal *analog multimeter* is used. The main problem with an analog signal is continuously varying with respect to time; the person has to be expert in *Time domain analysis* to find out perfect result.

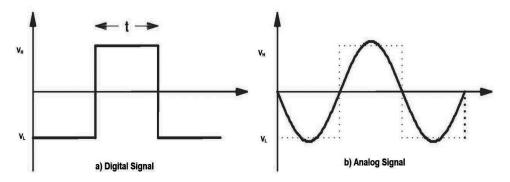

## 1.2.2 Digital system:

To overcome the problems of an analog system; the digital system developed. Digital system requires digital information. Digital information

can be represented by fixed number of non – continuous or discrete symbols called as *Digits*. In digital system binary system is used which has only two digits "0" and "1".

**Binary system:** as we are using binary in digital system which restricts the digital signal to have only two distinct values.

#### **Advantages of Binary system:**

- 1. Most information processing systems are constructed by using switches (binary devices).

- 2. Binary signal are more reliable.

- 3. The basic decision making processes required of digital systems are binary.

**Bits:** As binary quantities are encountered in many different physical forms, it is convenient to have a common way of representing binary states by using digit symbols "0" and "1" to represent two possible values of binary quantity at any time. These symbols are called as "bits", abbreviation of term "**Bi**nary digits". Fig. 1.2.2 shows digital and analog signal. We use "1" to denote "IGH" and "0" to denote "LOW" level of the signal. Binary voltage values  $V_H$  and  $V_L$  are represented as "1" and "0" respectively.

#### **Convention:**

In binary system two states 1 and 0 are present. The voltage levels are predefined by the manufactures of chip and user cannot change it. Generally HIGH LOGIC =  $1 = V_{CC} = +5$  volt and LOW LOGIC = 0 = GND = 0 volt Currently we are in the digital world. The widest application of digital system is computers and to learn inside of the computers digital system is the base also it is easy to implement and in around 90% cases you will find that analog systems are replaced by digital systems.

## 1.3 NUMBERING SYSTEM

We will begin our discussion on various number systems by briefly describing the parameters that are common to all number systems.

#### **Positional Number:**

A number system is defined by digits or numerals. We can combine digits as per our requirement to represent full range. The number system with which we are normally familiar is Arabic Numerals, consists of 10 digits such as  $0, 1, 2, \ldots, 9$ .

#### **Decimal Number System:**

The 10 Arabic digits can be combined in various ways to represent any number. Fundamental way of constructing a number is to form a sequence or string of digits in which consecutive digits represent consecutive power of 10. For example take 3 digit number 876. The 876 represent, from left to right, hundreds (8), tens (7) and unit (6).

We can decompose the number as

$$876 = 8 \times 10^2 + 7 \times 10^1 + 6 \times 10^0$$

... (1)

This system is decimal number system which is a good example of **positional number** system. Here each digit of multi-digit number has fixed value (or weight) determined by its position. The number is also called as **weighted number system**. Presently in the above example we have considered only integer part. One may require to represent fractional part also. Here fractional part is denoted by sequences of digits whose weights are negative powers of 10. The integer part and fractional part represents the full number for example 1.414, both integer and fractional part are separated by special symbol '.' called a decimal point.

The number can be decomposed as

$$1.414 = 1 \times 10^{0} + 4 \times 10^{-1} + 1 \times 10^{-2} + 4 \times 10^{-3}$$

... (2)

#### **Number Base:**

The decimal number notation can be written in generalized form where quantity **10** is replaced by **'r'** called as **base** or **radix**, of the number system.

We will represent number

$$\mathbf{x_2} \ \mathbf{x_1} \ \mathbf{x_0} \cdot \mathbf{x^{-1}} \ \mathbf{x^{-2}}$$

as  $\mathbf{x_2} \ \mathbf{x_1} \ \mathbf{x_0} \cdot \mathbf{x_{-1}} \ \mathbf{x_{-2}} = \mathbf{x_2} \ \mathbf{X} \ \mathbf{r^2} + \mathbf{x_1} \ \mathbf{X} \ \mathbf{r^1} + \mathbf{x_0} \ \mathbf{X} \ \mathbf{r^0} \cdot \mathbf{x_{-1}} \ \mathbf{X} \ \mathbf{r^{-1}} + \mathbf{x_{-2}} \ \mathbf{X} \ \mathbf{r^{-2}} \dots (3)$

Following table shows various number systems of our interest.

| System Name | Base 'r' | Digits / symbols used in the system |

|-------------|----------|-------------------------------------|

| Decimal     | 10       | 0, 1, 2, 3, 4, 5, 6, 7, 8, 9        |

| Binary      | 2  | 0, 1                                      |

|-------------|----|-------------------------------------------|

| Octal       | 8  | 0, 1, 2, 3, 4, 5, 6, 7                    |

| Hexadecimal | 16 | 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, |

|             |    | E, F                                      |

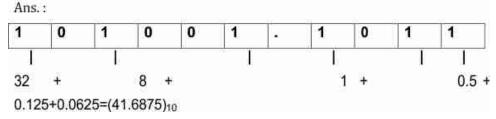

## 1.3.1 Binary number system:

We have already seen that binary number system has base / radix 2, which means it has only two digits, namely "0" and "1". The weights for binary number can be given by

| Binary number | $2^4$ | $2^3$ | $2^2$ | $2^{1}$ | $2^{0}$ | 2 <sup>-1</sup> | $2^{-2}$ | $2^{-3}$ | ••• |

|---------------|-------|-------|-------|---------|---------|-----------------|----------|----------|-----|

| Equivalent    | 16    | 8     | 4     | 2       | 1       | 0.5             | 0.25     | 0.125    |     |

| decimal       |       |       |       |         |         |                 |          |          |     |

By putting

$$r = 2$$

in equation (3) we can get equation for binary as follows  $x_2 \times 2^2 + x_1 \times 2^1 + x_0 \times 2^0 + x_{-1} \times 2^{-1} + x_{-2} \times 2^{-2} \dots$  (4)

Let's have one example, If Binary number is  $(101)_2$ , then  $x_2 x_1 x_0 = 101$

$$x_2 \times 2^2 + x_1 \times 2^1 + x_0 \times 2^0$$

=  $1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0$

=  $4 + 0 + 1 = (5)_{10}$

$\therefore (101)_2 = (5)_{10}$

## 1.3.2 Octal number system:

The octal number system has a base 8 and consists of 8 different digits or symbols such as 0 to 7. As there are 8 digits, 3 bits  $(2^3 = 8)$  are sufficient to represent any octal number in binary format. Following table shows 3 bit binary equivalent for each octal number

| 3-bit binar | ry equivalent | Octal N | umber |

|-------------|---------------|---------|-------|

| 0           | 0             | 0       | 0     |

| 0           | 0             | 1       | 1     |

| 0           | 1             | 0       | 2     |

| 0           | 1             | 1       | 3     |

| 1           | 0             | 0       | 4     |

| 1           | 0             | 1       | 5     |

| 1           | 1             | 0       | 6     |

| 1           | 1             | 1       | 7     |

The weights for actual number system can be given by

| Octal      | $8^3$ | $8^2$ | 8 <sup>1</sup> | $8^0$ | 8-1   | 8-2     | 8-3     |  |

|------------|-------|-------|----------------|-------|-------|---------|---------|--|

| number     |       |       |                |       |       |         |         |  |

| Equivalent | 512   | 64    | 8              | 1     | 1/8 = | 1/64 =  | 1/512 = |  |

| decimal    |       |       |                |       | 0.125 | 0.01562 | 0.00195 |  |

By putting r = 8 in equation (4) we can get equation for octal as follows

$$x_2 \times 8^2 + x_1 \times 8^1 + x_0 \times 8^0 + x_{-1} \times 8^{-1} + x_{-2} \times 8^{-2}$$

... (5)

Let's have one example, If Octal number is  $(357)_8$ , then  $x_2 x_1 x_0 = 357$

$$x_2 \times 8^2 + x_1 \times 8^1 + x_0 \times 8^0$$

=  $3 \times 8^2 + 5 \times 8^1 + 7 \times 8^0$

=  $192 + 40 + 7 = (239)_{10}$

$\therefore (357)_8 = (239)_{10}$

#### 1.3.3 Hexadecimal number system:

The Hexadecimal number system has a base 16 and consists of 16 different digits or symbols. First ten digits or symbols are from decimal number system i.e. 0, 1, 2, ..., 9 and next six are A, B, C, D, E and F representing 10, 11, 12, 13, 14 and 15 respectively. As there are 16 digits or symbols, 4 bits  $(2^4 = 16)$  are sufficient to represent any hexadecimal number in binary format. Following table shows 4 bit binary equivalent for each hexadecimal number.

| 4-bit | binary equivalent | Hexade | cimal Nu | mber   |

|-------|-------------------|--------|----------|--------|

| 0     | 0                 | 0      | 0        | 0      |

| 0     | 0                 | 0      | 1        | 1      |

| 0     | 0                 | 1      | 0        | 2      |

| 0     | 0                 | 1      | 1        | 3      |

| 0     | 1                 | 0      | 0        | 4      |

| 0     | 1                 | 0      | 1        | 5      |

| 0     | 1                 | 1      | 0        | 6      |

| 0     | 1                 | 1      | 1        | 7      |

| 1     | 0                 | 0      | 0        | 8      |

| 1     | 0                 | 0      | 1        | 9      |

| 1     | 0                 | 1      | 0        | 10 = A |

| 1     | 0                 | 1      | 1        | 11 = B |

| 1     | 1                 | 0      | 0        | 12 = C |

| 1     | 1                 | 0      | 1        | 13 = D |

| 1     | 1                 | 1      | 0        | 14 = E |

| 1     | 1                 | 1      | 1        | 15 = F |

The weights for actual number system can be given by:

| Hexadecimal | $16^2$ | 16 <sup>1</sup> | $16^{0}$ | 16-1         | 16-2            | ••• |

|-------------|--------|-----------------|----------|--------------|-----------------|-----|

| number      |        |                 |          |              |                 |     |

| Equivalent  | 256    | 16              | 1        | 1/16= 0.0625 | 1/256 = 0.00390 |     |

| decimal     |        |                 |          |              |                 |     |

By putting r = 16 in equation (5) we can get equation for hexadecimal as follows

$$x_2 \times 16^2 + x_1 \times 16^1 + x_0 \times 16^0 + x_{-1} \times 16^{-1} + x_{-2} \times 16^{-2} \dots (6)$$

Let's have one example, If Hexadecimal number is (1AF)<sub>16</sub>, then

$$x_2 x_1 x_0 = 1 A F$$

$x_2 x 16^2 + x_1 x 16^1 + x_0 x 16^0$

$= 1 x 16^2 + A x 16^1 + F x 16^0$

$= 256 + (10 x 16) + (15 x 1)$

$= 256 + 160 + 15 = (431)_{10}$

$\therefore (1AF)_{16} = (431)_{10}$

# 1.4 CONVERSION FROM ONE NUMBER SYSTEM TO ANOTHER

In this section we are going to study conversion from one type of number system to another i.e. decimal to binary / octal / hexadecimal or vice versa and hexadecimal to octal, hexadecimal to binary, binary to octal etc.

There are many methods or techniques which can be used to convert numbers from one base to another. In this chapter, we'll demonstrate the following

Decimal to Other Base System

- Other Base System to Decimal

- Other Base System to Non-Decimal

- Binary to Octal

- Octal to Binary

- Binary to Hexadecimal

- Hexadecimal to Binary

## 1.4.1 Decimal to Other Base System:

- **Step 1**: Divide the decimal number to be converted by the value of the new base.

- **Step 2**: Get the remainder from Step 1 as the rightmost digit (least significant digit) of the new base number.

- **Step 3**: Divide the quotient of the previous divide by the new base.

- **Step 4**: Record the remainder from Step 3 as the next digit (to the left) of the new base number.

Repeat Steps 3 and 4, getting remainders from right to left, until the quotient becomes zero in Step 3.

The last remainder thus obtained will be the Most Significant Digit (MSD) of the new base number.

## **Example:**

Decimal Number: 29<sub>10</sub>

#### **Calculating Binary Equivalent:**

| Step   | Operation | Result | Remainder |

|--------|-----------|--------|-----------|

| Step 1 | 29 / 2    | 14     | 1         |

| Step 2 | 14 / 2    | 7      | 0         |

| Step 3 | 7/2       | 3      | 1         |

| Step 4 | 3/2       | 1      | 1         |

| Step 5 | 1/2       | 0      | 1         |

As mentioned in Steps 2 and 4, the remainders have to be arranged in the reverse order so that the first remainder becomes the Least Significant Digit (LSD) and the last remainder becomes the Most Significant Digit (MSD).

Decimal Number :  $29_{10}$  = Binary Number :  $11101_2$

#### **1.4.2 Other Base System to Decimal System:**

- **Step 1**: Determine the column (positional) value of each digit (this depends on the position of the digit and the base of the number system).

- **Step 2**: Multiply the obtained column values (in Step 1) by the digits in the corresponding columns.

- **Step 3**: Sum the products calculated in Step 2. The total is the Equivalent value in decimal.

#### **Example:**

Binary Number: 11101<sub>2</sub>

#### **Calculating Decimal Equivalent:**

| Step   | Binary             | Decimal Number                                                                              |

|--------|--------------------|---------------------------------------------------------------------------------------------|

|        | Number             |                                                                                             |

| Step 1 | 11101 <sub>2</sub> | $((1 \times 2^4) + (1 \times 2^3) + (1 \times 2^2) + (0 \times 2^1) + (1 \times 2^0))_{10}$ |

| Step 2 | 11101 <sub>2</sub> | $(16+8+4+0+1)_{10}$                                                                         |

| Step 3 | 11101 <sub>2</sub> | 29 <sub>10</sub>                                                                            |

**Binary Number :**  $11101_2$  = Decimal Number :  $291_0$

#### 1.4.3 Binary to Octal:

**Step 1**: Divide the binary digits into groups of three (starting from the right).

**Step 2**: Convert each group of three binary digits to one octal digit.

## Example:

Binary Number: 10101<sub>2</sub> Calculating Octal Equivalent:

| Step   | Binary Number | Octal Number |

|--------|---------------|--------------|

| Step 1 | 101012        | 010 101      |

| Step 2 | 101012        | 28 58        |

| Step 3 | 101012        | 258          |

**Binary Number :**  $10101_2$  = Octal Number :  $25_8$

## 1.4.4 Octal to Binary:

**Step 1**: Convert each octal digit to a 3-digit binary number (the octal digits may be treated as decimal for this conversion).

**Step 2**: Combine all the resulting binary groups (of 3 digits each) into a single binary number.

## **Example:**

Octal Number: 25<sub>8</sub>

Calculating Binary Equivalent:

| Step   | Octal Number    | <b>Binary Number</b> |

|--------|-----------------|----------------------|

| Step 1 | 25 <sub>8</sub> | $2_{10}  5_{10}$     |

| Step 2 | 258             | $010_2\ 101_2$       |

| Step 3 | 258             | 0101012              |

Octal Number :  $25_8$  = Binary Number :  $10101_2$

#### 1.4.5 Hexadecimal to Binary:

**Step 1:** Convert each hexadecimal digit to a 4-digit binary number (the hexadecimal digits may be treated as decimal for this conversion).

**Step 2 :** Combine all the resulting binary groups (of 4 digits each) into a single binary number.

#### **Example:**

Hexadecimal Number: 15<sub>16</sub>

Calculating Binary Equivalent

| Step   | Hexadecimal Number | Binary Number    |

|--------|--------------------|------------------|

| Step 1 | 15 <sub>16</sub>   | $1_{10}  5_{10}$ |

| Step 2 | 15 <sub>16</sub>   | 00012 01012      |

| Step 3 | 15 <sub>16</sub>   | 000101012        |

#### 1.5 FLOATING POINT NUMBER

Floating point numbers are used to represent non integer fractional numbers and are used in technical calculations. E.g. 3.256, 2.1 and 0.0036.

The most commonly used floating point standard is the IEEE standard.

According to this standard, floating point numbers are represented with 32 bits (single precision) or 64 bits (double precision).

It is an arithmetic operations consist of addition, subtraction, multiplication and division.

These operations are done with algorithms similar to those used on sign magnitude integers (because of the similarity of representation) example, only add numbers of the same sign. If the numbers are of opposite sign, must do subtraction.

#### **Addition:**

**Example on decimal value given in scientific notation:**

First step: align decimal points

Second step: add

(presumes use of infinite precision, without regard for accuracy)

**Third step:** normalize the result (already normalized!)

#### **Example on fl pt. value given in binary:**

|     |   | S | Е        | F                                       |

|-----|---|---|----------|-----------------------------------------|

| .25 | = | 0 | 01111101 | 000000000000000000000000000000000000000 |

| 100 | = | 0 | 10000101 | 100100000000000000000000000000000000000 |

to add these fl. pt. representations,

**Step 1:** align radix points

shifting the mantissa LEFT by 1 bit DECREASES THE EXPONENT by 1 shifting the mantissa RIGHT by 1 bit INCREASES THE EXPONENT by 1  $\,$

we want to shift the mantissa right, because the bits that fall off the end should come from the least significant end of the mantissa

- -> choose to shift the .25, since we want to increase it's exponent.

- -> shift by 10000101

01111101

-----

00001000 (8) places.

with hidden bit and radix point shown, for clarity

(note that hidden bit is shifted into msb of mantissa)

- **Step 2:** add (don't forget the hidden bit for the 100)

- 0 10000101 1.10010000000000000000000 (100)

- + 0 10000101 0.0000000100000000000000 (.25)

\_\_\_\_\_

0 10000101 1.100100010000000000000000

**Step 3:** normalize the result (get the "hidden bit" to be a 1) it already is for this example.

result is

0 10000101 100100010000000000000000

suppose that the result of an addition of aligned mantissas gives

and the exponent to go with this is 10000000.

We must put the mantissa back in the normalized form. Shift the mantissa to the right by one place, and increase the exponent by 1.

The exponent and mantissa become

#### **Subtraction:**

Like addition as far as alignment of radix points then the algorithm for subtraction of sign mag. numbers takes over.

Before subtracting,

- Compare magnitudes (don't forget the hidden bit!)

- Change sign bit if order of operands is changed.

Don't forget to normalize number afterward.

## Example:

- 0 10000000 111000000000000000000000

\_\_\_\_\_

## **Step 1:** align radix points

$0\ 10000000\ 1110000000000000000000000$

becomes

$0\ 10000001\ 1.100100010000000000000000$

-----

**Step 2 :** subtract mantissa

1.100100010000000000000000

-----

0.101000010000000000000000

**Step 3:** put result in normalized form

Shift mantissa left by 1 place, implying a subtraction of 1 from the exponent.

$0\ 10000000\ 010000100000000000000000$

#### **Multiplication:**

example on decimal values given in scientific notation:

algorithm: multiply mantissas add exponents

**example in binary:** use a mantissa that is only 4 bits so that I don't spend all day just doing the multiplication part.

```

0 10000100 0100

1 00111100 1100

1.0100

mantissa multiplication:

(don't forget hidden bit)

x 1.1100

00000

00000

10100

10100

10100

_____

1000110000

10.00110000

becomes

add exponents: always add true exponents (otherwise the bias gets added

in twice)

biased:

10000100

+ 00111100

10000100

01111111

(switch the order of the subtraction,

- 01111111

- 00111100

so that we can get a negative value)

00000101

01000011

true exp

true exp

is 5.

is -67

add true exponents 5 + (-67) is -62.

re-bias exponent: -62 + 127 is 65.

unsigned representation for 65 is 01000001.

put the result back together (and add sign bit).

1 01000001 10.00110000

normalize the result:

(moving the radix point one place to the left increases

the exponent by 1.)

1 01000001 10.00110000

becomes

1 01000010 1.000110000

this is the value stored (not the hidden bit!):

```

1 01000010 000110000

#### **Division:**

It is similar to multiplication.

#### true division:

- do unsigned division on the mantissas (don't forget the hidden bit)

- subtract TRUE exponents

The IEEE standard is very specific about how all this is done. Unfortunately, the hardware to do all this is pretty slow.

#### Some comparisons of approximate times:

- 2's complement integer add 1 time unit

- fl. pt add 4 time units

- fl. pt multiply 6 time units

- fl. pt. Divide 13 time units

There is a faster way to do division. It is called division by reciprocal approximation. It takes about the same time as a fl. pt. multiply. Unfortunately, the results are not always the same as with true division.

## Division by reciprocal approximation:

instead of doing a / b

they do a x 1/b.

figure out a reciprocal for b, and then use the fl. pt.

multiplication hardware.

example of a result that isn't the same as with true division.

true division: 3/3 = 1 (exactly) reciprocal approx: 1/3 = .333333333

It is not always possible to get a perfectly accurate reciprocal

# 1.6 WEIGHTED CODES BINARY CODED DECIMAL, NON-WEIGHTED CODES EXCESS 3 CODE

**Binary code:** The digital data is represented, stored and transmitted as group of binary bits. This group is also called as binary code.

- The binary code is represented by the number as well as alphanumeric letter.

- The group of symbols is called as a code.

#### **Binary Codes for Decimal digits:**

The following table shows the various binary codes for decimal digits 0 to 9

| Decimal | 8421 Code | 2421 Code | 84-2-1 Code | Excess 3 Code |

|---------|-----------|-----------|-------------|---------------|

| Digit   |           |           |             |               |

| 0       | 0000      | 0000      | 0000        | 0011          |

| 1       | 0001      | 0001      | 0111        | 0100          |

| 2       | 0010      | 0010      | 0110        | 0101          |

| 3       | 0011      | 0011      | 0101        | 0110          |

| 4       | 0100      | 0100      | 0100        | 0111          |

| 5       | 0101      | 1011      | 1011        | 1000          |

| 6       | 0110      | 1100      | 1010        | 1001          |

| 7       | 0111      | 1101      | 1001        | 1010          |

| 8       | 1000      | 1110      | 1000        | 1011          |

| 9       | 1001      | 1111      | 1111        | 1100          |

We have 10 digits in decimal number system. To represent these 10 digits in binary, we require minimum of 4 bits. But, with 4 bits there will be 16 unique combinations of zeros and ones. Since, we have only 10 decimal digits, the other 6 combinations of zeros and ones are not required.

#### 8 4 2 1 code:

- The weights of this code are 8, 4, 2 and 1.

- This code has all positive weights. So, it is a positively weighted code.

- This code is also called as natural BCD Binary Coded decimal code

#### **Example:**

Let us find the BCD equivalent of the decimal number 786. This number has 3 decimal digits 7, 8 and 6. From the table, we can write the BCD 84218421 codes of 7, 8 and 6 are 0111, 1000 and 0110 respectively.

$$\therefore$$

78678610 = 011110000110011110000110BCD

There are 12 bits in BCD representation, since each BCD code of decimal digit has 4 bits.

#### 2 4 2 1 code:

- The weights of this code are 2, 4, 2 and 1.

- This code has all positive weights. So, it is a positively weighted code.

- It is an unnatural BCD code. Sum of weights of unnatural BCD codes is equal to 9.

• It is a self-complementing code. Self-complementing codes provide the 9's complement of a decimal number, just by interchanging 1's and 0's in its equivalent 2421 representation.

#### **Example:**

Let us find the 2421 equivalent of the decimal number 786. This number has 3 decimal digits 7, 8 and 6. From the table, we can write the 2421 codes of 7, 8 and 6 are 1101, 1110 and 1100 respectively.

Therefore, the 2421 equivalent of the decimal number 786 is 110111101100.

#### 8 4 -2 -1 code:

- The weights of this code are 8, 4, -2 and -1.

- This code has negative weights along with positive weights. So, it is a negatively weighted code.

- It is an unnatural BCD code.

- It is a self-complementing code.

#### **Example:**

Let us find the 8 4-2-1 equivalent of the decimal number 786. This number has 3 decimal digits 7, 8 and 6. From the table, we can write the 8 4-2-1 codes of 7, 8 and 6 are 1001, 1000 and 1010 respectively.

Therefore, the  $8\ 4\ -2\ -1$  equivalent of the decimal number 786 is 100110001010.

#### Excess 3 code:

- This code doesn't have any weights. So, it is an un-weighted code.

- We will get the Excess 3 code of a decimal number by adding three 00110011 to the binary equivalent of that decimal number. Hence, it is called as Excess 3 code.

- It is a self-complementing code.

## **Example:**

Let us find the Excess 3 equivalent of the decimal number 786. This number has 3 decimal digits 7, 8 and 6. From the table, we can write the Excess 3 codes of 7, 8 and 6 are 1010, 1011 and 1001 respectively.

Therefore, the Excess 3 equivalent of the decimal number 786 is 101010111001

## 1.7 GRAY CODE

A binary code used to represent digits generated from a mechanical sensor that may be prone to error. Used in telegraphy in the late 1800s, and also known as "reflected binary code," Gray code was patented by Bell Labs researcher Frank Gray in 1947.

#### **Only Change One Bit:**

In Gray code, there is only one bit location different between numeric increments, which make mechanical transitions from one digit to the next less error prone.

The following table shows the 4-bit Gray codes corresponding to each 4-bit binary code.

| Decimal<br>Number | Binary Code | Gray Code |

|-------------------|-------------|-----------|

| 0                 | 0000        | 0000      |

| 1                 | 0001        | 0001      |

| 2                 | 0010        | 0011      |

| 3                 | 0011        | 0010      |

| 4                 | 0100        | 0110      |

| 5                 | 0101        | 0111      |

| 6                 | 0110        | 0101      |

| 7                 | 0111        | 0100      |

| 8                 | 1000        | 1100      |

| 9                 | 1001        | 1101      |

| 10                | 1010        | 1111      |

| 11                | 1011        | 1110      |

| 12                | 1100        | 1010      |

| 13                | 1101        | 1011      |

| 14                | 1110        | 1001      |

| 15                | 1111        | 1000      |

- This code doesn't have any weights. So, it is an un-weighted code.

- In the above table, the successive Gray codes are differed in one bit position only. Hence, this code is called as unit distance code.

#### **Binary code to Gray Code Conversion:**

Follow these steps for converting a binary code into its equivalent Gray code.

- Consider the given binary code and place a zero to the left of MSB.

- Compare the successive two bits starting from zero. If the 2 bits are same, then the output is zero. Otherwise, output is one.

- Repeat the above step till the LSB of Gray code is obtained.

#### **Example:**

From the table, we know that the Gray code corresponding to binary code 1000 is 1100. Now, let us verify it by using the above procedure.

Given, binary code is 1000.

**Step 1 :** By placing zero to the left of MSB, the binary code will 01000.

**Step 2 :** By comparing successive two bits of new binary code, we will get the gray code as 1100.

## 1.8 ALPHANUMERIC CODES

Alphanumeric codes are sometimes called character codes due to their certain properties. Now these codes are basically binary codes. We can write alphanumeric data, including data, letters of the alphabet, numbers, mathematical symbols and punctuation marks by this code which can be easily understandable and can be processed by the computers. Input output devices such as keyboards, monitors, mouse can be interfaced using these codes. 12-bit Hollerith code is the better known and perhaps the first effective code in the days of evolving computers in early days. During this period punch cards were used as the inputting and outputting data. But nowadays these codes are termed obsolete as many other modern codes have evolved. The most common alphanumeric codes used these days are ASCII code, EBCDIC code and Unicode. Now we will discuss about them briefly.

#### 1.8.1 ASCII code:

The full form of ASCII code is American Standard Code for Information Interchange. It is a seven bit code based on the English alphabet.

In 1967 this code was first published and since then it is being modified and updated. ASCII code has 128 characters some of which are enlisted below to get familiar with the code.

| DEC | OCT | HEX | BIN      | Symbol | Description         |

|-----|-----|-----|----------|--------|---------------------|

| 0   | 000 | 00  | 00000000 | NUL    | Null char           |

| 1   | 001 | 01  | 00000001 | SOH    | Start of Heading    |

| 2   | 002 | 02  | 00000010 | STX    | Start of Text       |

| 3   | 003 | 03  | 00000011 | ETX    | End of Text         |

| 4   | 004 | 04  | 00000100 | EOT    | End of Transmission |

| 5   | 005 | 05  | 00000101 | ENQ    | Enquiry             |

| 6   | 006 | 06  | 00000110 | ACK    | Acknowledgment      |

| 7   | 007 | 07  | 00000111 | BEL    | Bell                |

| 8   | 010 | 08  | 00001000 | BS     | Back Space          |

| 9  | 011 | 09 | 00001001 | HT | Horizontal Tab   |

|----|-----|----|----------|----|------------------|

| 10 | 012 | 0A | 00001010 | LF | Line Feed        |

| 11 | 013 | 0B | 00001011 | VT | Vertical Tab     |

| 12 | 014 | 0C | 00001100 | FF | Form Feed        |

| 13 | 015 | 0D | 00001101 | CR | Carriage Return  |

| 14 | 016 | 0E | 00001110 | SO | Shift Out / X-On |

| 15 | 017 | 0F | 00001111 | SI | Shift In / X-O   |

There are many more codes which are not included here.

#### **1.8.2 EBCDIC:**

The EBCDIC stands for Extended Binary Coded Decimal Interchange Code. IBM invented this code to extend the Binary Coded Decimal which existed at that time. All the IBM computers and peripherals use this code. It is an 8 bit code and therefore can accommodate 256 characters. Below is given some characters of EBCDIC code to get familiar with it.

| C | EBCDIC       | HEX | Cha | EBCDIC    | HE | Char      | EBCDIC    | HEX |

|---|--------------|-----|-----|-----------|----|-----------|-----------|-----|

| h |              |     | r   |           | X  |           |           |     |

| a |              |     |     |           |    |           |           |     |

| r |              |     |     |           |    |           |           |     |

| A | 1100<br>0001 | C1  | P   | 1101 0111 | D7 | 4         | 1111 0100 | F4  |

| В | 1100<br>0010 | C2  | Q   | 1101 1000 | D8 | 5         | 1111 0101 | F5  |

| С | 1100<br>0011 | C3  | R   | 1101 1001 | D9 | 6         | 1111 0110 | F6  |

| D | 1100<br>0100 | C4  | S   | 1110 0010 | E2 | 7         | 1111 0111 | F7  |

| Е | 1100<br>0101 | C5  | Т   | 1110 0011 | E3 | 8         | 1111 1000 | F8  |

| F | 1100<br>0110 | C6  | U   | 1110 0100 | E4 | 9         | 1111 1001 | F9  |

| G | 1100<br>0111 | C7  | V   | 1110 0101 | E5 | blan<br>k |           |     |

| Н | 1100<br>1000 | C8  | W   | 1110 0110 | E6 | •         | •••       | ••• |

| I | 1100<br>1001 | C9  | X   | 1110 0111 | E7 | (         | •••       |     |

| J | 1101<br>0001 | D1  | Y   | 1110 1000 | E8 | +         | •••       | ••• |

| K | 1101<br>0010 | D2  | Z   | 1110 1001 | E9 | \$        |           |     |

| L | 1101         | D3  | 0   | 1111 0000 | F0 | *         | •••       |     |

|   | 0011 |    |   |           |    |   |     |  |

|---|------|----|---|-----------|----|---|-----|--|

| M | 1101 | D4 | 1 | 1111 0001 | F1 | ) | ••• |  |

|   | 0100 |    |   |           |    |   |     |  |

| N | 1101 | D5 | 2 | 1111 0010 | F2 | _ | ••• |  |

|   | 0101 |    |   |           |    |   |     |  |

| O | 1101 | D6 | 3 | 1111 0011 | F3 |   |     |  |

|   | 0110 |    |   |           |    |   |     |  |

#### 1.8.3 ISCII Code:

ISCII stands for Indian Script Code for Information Interchange. IISCII was developed to support Indian languages on computer. Language supported by IISCI include Devanagari, Tamil, Bangla, Gujarati, Gurmukhi, Tamil, Telugu, etc. IISCI is mostly used by government departments and before it could catch on, a new universal encoding standard called Unicode was introduced.

#### 1.8.4 Hollerith code:

In 1896, Herman Hollerith formed a company called the Tabulating Machine Company. This company developed a line of machines that used punched cards for tabulation. After a number of mergers, this company was formed into the IBM, Inc. We often refer to the punched-cards used in computer systems as Hollerith cards and the 12-bit code used on a punched-card is called the Hollerith code.

A Hollerith string is a sequence of 12-bit characters; they are encoded as two ASCII characters, containing 6 bits each. The first character contains punches 12,0,2,4,6,8 and the second character contains punches 11, 1, 3, 5, 7, 9. Interleaving the two characters gives the original 12 bits. To make the characters printable on ASCII terminals, bit 7 is always set to 0 and bit 6 is said to the complement of bit 5. These two bits are ignored when reading Hollerith cards.

Today, as punched cards are mostly obsolete and replaced with other storage medias so the Hollerith code is rendered obsolete.

#### 1.8.5 Morse code:

The Morse code, invented in 1837 by Samuel F.B. Morse, was the first alphanumeric code used in telecommunication. It uses a standardized sequence of short and long elements to represent letters, numerals and special characters of a given message. The short and long elements can be formed by sounds, marks, pulses, on off keying and are commonly known as dots and dashes. For example: The letter "A" is formed by a dot followed by a dash. The digit 5 is formed by 5 dots in succession. The

International Morse code treats a dash equal to three dots. To see the details of Morse code table you can refer the Internet search engines.

Due to variable length of Morse code characters, the morse code could not adapt to automated circuits. In most electronic communication, the Baudot code and ASCII code are used.

Morse code has limited applications. It is used in communication using telegraph lines, radio circuits. Pilots and air traffic controllers also use them to transmit their identity and other information

#### 1.8.6 Teletypewriter (TTY):

A teletypewriter (TTY) is an input device that allows alphanumeric character to be typed in and sent, usually one at a time as they are typed, to a computer or a printer. The Teletype Corporation developed the teletypewriter, which was an early interface to computers. Teletype mode is the capability of a keyboard, computer, application, printer, display, or modem to handle teletypewriter input and output. Basically, this is a one-character-at-a-time mode of sending, receiving, or handling data, although it is often modified to handle a line of characters at a time. Since this mode requires little programming logic, it is often used where memory is limited. The Basic Input/Output Operating System (BIOS) sends messages to a PC display using teletype mode. Most printers offer a teletype mode. The simplest video display output format is text in teletype mode. Many modems today continue to include support for a TTY interface.

## 1.9 ERROR DETECTION AND CORRECTION

#### What is Error?:

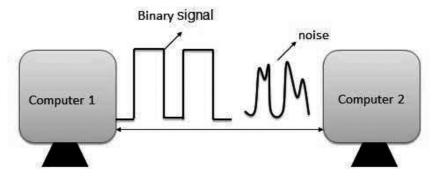

Error is a condition when the output information does not match with the input information. During transmission, digital signals suffer from noise that can introduce errors in the binary bits travelling from one system to other. That means a 0 bit may change to 1 or a 1 bit may change to 0.

#### **Error-Detecting codes:**

Whenever a message is transmitted, it may get scrambled by noise or data may get corrupted. To avoid this, we use error-detecting codes which are additional data added to a given digital message to help us detect if an error occurred during transmission of the message. A simple example of error-detecting code is parity check.

#### **Error-Correcting codes:**

Along with error-detecting code, we can also pass some data to figure out the original message from the corrupt message that we received. This type of code is called an error-correcting code. Error-correcting codes also deploy the same strategy as error-detecting codes but additionally, such codes also detect the exact location of the corrupt bit.

In error-correcting codes, parity check has a simple way to detect errors along with a sophisticated mechanism to determine the corrupt bit location. Once the corrupt bit is located, its value is reverted (from 0 to 1 or 1 to 0) to get the original message

#### 1.10 UNIVERSAL PRODUCT CODE

A UPC, short for universal product code, is a type of code printed on retail product packaging to aid in identifying a particular item. It consists of two parts – the machine-readable barcode, which is a series of unique black bars, and the unique 12-digit number beneath it.

The purpose of UPCs is to make it easy to identify product features, such as the brand name, item, size, and color, when an item is scanned at checkout. In fact, that's why they were created in the first place – to speed up the checkout process at grocery stores. UPCs are also helpful in tracking inventory within a store or warehouse.

To obtain a UPC for use on a product a company has to first apply to become part of the system. GS1 US, the Global Standards Organization, formerly known as the Uniform Code Council, manages the assigning of UPCs within the US.

#### Parts of a UPC:

After paying a fee to join, GS1 assigns a 6-digit manufacturer identification number, which becomes the first six digits in the UPC on all the company's products. That number identifies the particular manufacturer of the item.

The next five digits of the UPC is called an item number. It refers to the actual product itself. Within each company is a person responsible for issuing item numbers, to ensure that the same number isn"t used more than once and that old numbers referring to discontinued products are phased out.

Many consumer products have several variations, based on, for example, size, flavor, or color. Each variety requires its own item number. So a box of 24 one-inch nails has a different item number than a box of 24 two-inch nails, or a box of 50 one-inch nails.

The last digit in the 12-digit UPC is called the check digit. It is the product of several calculations – adding and multiplying several digits in the code – to confirm to the checkout scanner that the UPC is valid. If the check digit code is incorrect, the UPC won't scan properly.

#### **Advantages of UPCs:**

- UPCs have a number of advantages to businesses and consumers. Because they make it possible for barcode scanners to immediately identify a product and its associated price, UPCs improve speed.

- They improve efficiency and productivity, by eliminating the need to manually enter product information.

- They also make it possible to track inventory much more accurately than hand counting, to know when more product is needed on retail shelves or in warehouses. Or when there is an issue with a particular product and consumers who purchased it need to be alerted or a recall issued, UPCs allow products to be tracked through production to distribution to retail stores and even into consumer homes.

#### 1.11 CODE CONVERSION

#### In this section we are going to lean the following code conversions:

1 Binary to BCD 2 BCD to Binary

3 BCD to Excess-3 4 Excess-3 to BCD

#### 1.11.1 Binary to BCD:

For the binary to BCD conversation the steps to be followed are as given below:

Step 1 : Convert the binary number to decimalStep 2 : Convert decimal number into BCD

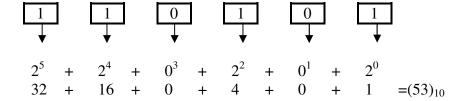

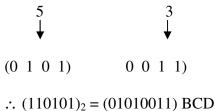

**Example:** Convert the binary number (110101)2 into BCD

**Solution:**

**Step 1 :** Convert the binary number to decimal

**Step 2:** Convert decimal number into BCD

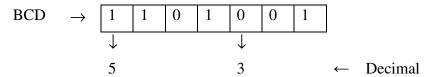

## 1.11.2 BCD to Binary:

Steps to be followed are as given below:

**Step 1 :** Convert the BCD number to decimal

Step 2: Convert decimal number into binary

**Example:** Convert the BCD number (0101 0011)BCD into binary

**Solution:**

**Step 1 :** Convert the BCD number to decimal

Step 2: Convert decimal number into binary

Use the long division method for decimal to binary conversation

$$(53)_{10}$$

=  $(110101)_2$

$(0101\ 0011)_{BCD}$  =  $(110\ 101)_2$

#### 1.11.3 BCD to Excess-3:

Steps to be followed are as given below:

Step 1: Convert BCD to decimal

**Step 2:** Add  $(3)^{10}$  to this decimal number

**Step 2:** Convert the decimal number of step 2 into binary, to get the excess -3 code

**Example:** Convert (1001)BCD to excess -3

**Solution:**

BCD

$$\begin{array}{c|ccccc}

1 & 0 & 0 & 1 \\

\downarrow & & & & \\

Decimal & 9 & & & \\

Add 3 & + & 3 & & \\

& & & & & \\

& & & & & \\

\hline

& & & & & \\

& & & & & \\

\hline

& & & & & \\

& & & & & \\

\hline

& & & & & \\

& & & & & \\

\hline

& & & & & \\

\hline

& & & & & \\

& & & & & \\

\hline

& & & & \\

\hline

& & & & & \\$$

Therefore :  $(1001)_{BCD} = (1100)e_{x-3}$

## 1.11.4 Excess-3 to BCD Conversion:

Subtract  $(0011)_2$  from each 4 bit excess-3 digit to obtain the corresponding BCD code.

| Given XS- 3 number           | 1001      | 1010                              |

|------------------------------|-----------|-----------------------------------|

| Subtract (0011) <sub>2</sub> | -0011     | 0011                              |

|                              | 11        | 111                               |

| BCD                          | 0110      | 0111                              |

|                              | (10011010 | $(0)_{XS-3} = (0110\ 0111)_{BCD}$ |

## **UNIT END QUESTIONS**

- 1. State the difference between analog and digital signals

- 2. Explain numbering system in brief

- 3. Explain floating point numbers with suitable example

- 4. Explain Universal Product Code

- 5. What is an error correction code?

- 6. Explain binary to decimal with suitable example

- 7. Explain decimal to binary with suitable example

- 8. Explain code conversion with suitable example

- 9. Convert the following fractional decimal numbers to equivalent binary number (show the step by step)

- **1.** 0.5682 **2.** 0.6954 **3.** 0.1235 **4.** 0.4754

\*\*\*\*

## **BINARY ARITHMETIC**

#### **Unit Structure**

- 2.0 Objectives

- 2.1 Introduction

- 2.2 Binary addition

- 2.3 Binary subtraction

- 2.4 Negative number representation2.4.1 Subtraction using 1's complement and 2's complement

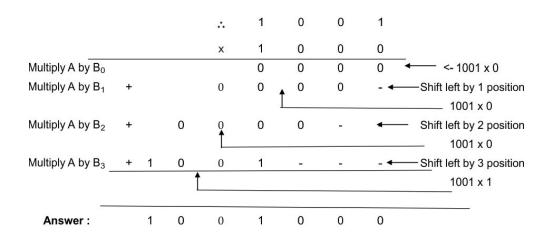

- 2.5 Binary multiplication

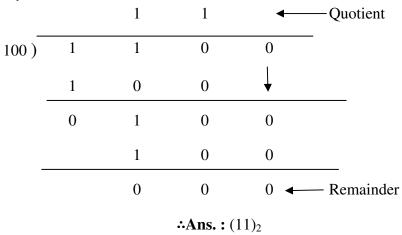

- 2.6 Binary division

- 2.7 Arithmetic in octal number system

- 2.8 Arithmetic in hexadecimal number system

- 2.9 BCD arithmetic

- 2.10 Excess 3 arithmetic

## 2.0 OBJECTIVE

This chapter would make you understand the following concepts

- What is binary arithmetic?

- Binary addition, subtraction, multiplication and division.

- Negative number representation

- Arithmetic in octal number system

- Arithmetic in hexadecimal number system

- BCD arithmetic

- Excess 3 arithmetic

- Examples on conversion

## 2.1 INTRODUCTION

Binary arithmetic is used in digital systems mainly because the numbers (decimal and floating-point numbers) are stored in binary format in most computer systems. All arithmetic operations such as addition, subtraction, multiplication, and division are done in binary representation of numbers. It is necessary to understand the binary number representation to figure out binary arithmetic in digital computers.

Binary arithmetic is essential part of all the digital computers and many other digital systems.

## 2.2 BINARY ADDITION

• Binary addition is the key for binary multiplication, subtraction and division. The four most basic cases of binary addition are shown in Table 2.1.

**Table 2.1: Four cases of binary addition:**

|        | Α |   | В | Addition | Comment                         |

|--------|---|---|---|----------|---------------------------------|

| Case 1 | 0 | + | 0 | 0 ]      | Same as decimal                 |

| Case 2 | 0 | + | 1 | 1 -      | Addition                        |

| Case 3 | 1 | + | 0 | 1 —      |                                 |

| Case 4 | 1 | + | 1 | 10       | • + • = • • = (10) <sub>2</sub> |

For cases 1, 2 and 3 of Table 2.1, the binary addition takes place by following the rules of decimal addition.

• But concentrate on case 4. Addition of binary 1 + 1 represent the combining of one pebble and one pebble to obtain a total of two pebble.

$$1 + 1 = \bullet \bullet \text{ two pebbles}$$

• Since binary 10 stands for • • two pebbles, the result of binary addition 1 + 1 is 10.

$$1 + 1 = (10)_2$$

#### 2.1.1 Sum and Carry:

- Thus, the fourth case yields a binary two (10). When the binary numbers are added, the fourth case in Table 2.1 creates a sum of 0 in the given column and a carry of 1 over to the next column.

- The four basic rules of binary addition in terms of sum and carry are as follows:

Table 2.2 Rules for binary addition

| Rule | A |   | В |   | Sum | Carry |

|------|---|---|---|---|-----|-------|

| 1    | 0 | + | 0 | = | 0   | 0     |

| 2    | 0 | + | 1 | = | 1   | 0     |

| 3    | 1 | + | 0 | = | 1   | 0     |

| 4    | 1 | + | 1 | = | 0   | 1     |

## 2.3 BINARY SUBTRACTION

#### **Rules for subtraction:**

In order to understand the binary subtraction, we should remember some of the important rules of decimal subtraction. They are as follows:

1. To carry out the subtraction (A - B) where A and B are the two single digit decimal numbers. We have to consider two cases,

## 2. Case I : Digit A > Digit B :

Let A =

$$(5)_{10}$$

and B =  $(3)_{10}$

Then A-B =  $(\bullet \bullet \bullet \bullet \bullet) - (\bullet \bullet \bullet) = \bullet \bullet$

$\div (5)_{10} - (3)_{10}$  =  $(2)_{10}$

## 3. Case II : Digit A < Digit B :

If A = (3)10 and B = (5)10 then we cannot perform (3 - 5) because we cannot take out 5 pebbles from 3. **Therefore, we have to borrow 1.** After borrowing, the subtraction is charged to,

$$13-5=8$$

Borrow

#### 2.3.1 Subtraction and Borrow:

• These two words will be used very frequently for the binary subtraction. For binary subtraction we have to remember the following four cases given in Table 2. 3

**Table 2.3: Four basic rules for binary subtraction:**

| Case | A |   | В | Subtraction | Borrow | Comment            |  |  |  |

|------|---|---|---|-------------|--------|--------------------|--|--|--|

| 1    | 0 | - | 0 | 0           | 0      | Same as decimal    |  |  |  |

| 2    | 1 | - | 0 | 1           | 0      | Same as decimal    |  |  |  |

| 3    | 1 | - | 1 | 0           | 0      | Same as decimal    |  |  |  |

| 4    | 0 | • | 1 | 1           | 1      | Borrow needs to be |  |  |  |

|      |   |   |   |             |        | taken              |  |  |  |

Consider case 4 in Table 2. 3. it is [0 - 1]. Hence a logic 1 borrowed.

This will change the subtraction from [0 - 1] to [10 - 1] that means [ •• - •] = • = 1.

## 2.4 NEGATIVE NUMBER REPRESENTATION

#### **Binary Subtraction using 1's and 2's Complements:**

- The direct binary subtraction becomes complicated as the number size increases.

- Therefore we can represent the subtraction of A B in the form of addition as: A+( B).

- We can represent number B (which is to be subtracted) in its 1's complement or 2's complement form and use addition instead of subtraction to get the result of A B.

## 2.4.1 Subtraction using 1's Complement :

The steps to be followed for subtraction  $(A)_2$  -  $(B)_2$  using 1's complement are as follows:

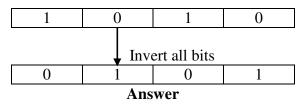

- **Step 1**: Convert number to be subtracted  $(B)_2$  to its 1's complement.

- **Step 2**: Add (A)<sub>2</sub> and 1's complement of (B)<sub>2</sub> using the rules of binary addition.

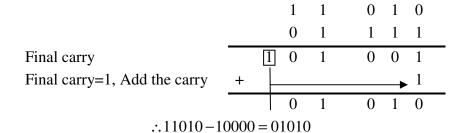

- **Step 3**: If final carry is 1, then add it to the result of addition obtained in step 2 to get the final result of (A)<sub>2</sub> (B)<sub>2</sub>. Note that if the final carry is 1 then the subtraction is positive and i in its true form.

- **Step 4**: If the final carry produced in step 2 is 0, then the result obtained in step 2 is negative and in the 1's complement form. So, convert it into the true form by complementing all the bits.

The following examples will make the concept of subtraction using 1"s complement crystal clear.

There are four possible cases depending on the magnitude and sign of the numbers involved.

Case 1: Number A and B, both positive and A > B.

Case 2: A and B both positive and A < B.

**Case 3:** Both numbers are negative.

Case 4: A = B.

Let us discuss them one by one.

Case 1 : A and B, both positive and A > B

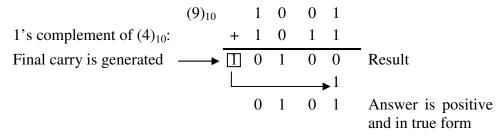

Ex. 2.1: Perform  $(9)_{10}$  -  $(4)_{10}$  using 1's complement method

Soln.:

Step1 : Convert  $(4)_{10}$  into 1's complement:

$$(4)_{10} = (0\ 1\ 0\ 0)_2$$

and 1's complement of  $(0100)_2 = (1\ 0\ 1\ 1)_2$

Step2: Add  $(9)_{10}$  and 1's complement of  $(4)_{10}$ :

### **Step 3:** Add the final carry to the result obtained in step 2:

Thus the answer is  $(0101)_2$ .

**Note:** When the final carry is produced the answer is positive and in its true form.

$(9)_{10}$  -  $(4)_{10}$  =  $(5)_{10}$  =  $(0101)_2$  which we have obtained.

## Case 2 : A and B both positive with A < B

**Ex.2.2**: Subtract  $(9)_{10}$  from  $(4)_{10}$  using 1's complement method

Soln.:

**Given :**

$$A = (4)_{10} = (0100)_2 B = (9)_{10} = (1001)_2$$

**Step 1**: Obtain 1's complement of  $(9)_{10}$ :

1's complement of  $(9)_{10}$  or  $(1001)_2$  is  $(0110)_2$ .

Step 2 : Add  $(4)_{10}$  and 1's complement of  $(9)_{10}$ .:

**Note:** As the final carry is 0, the answer is negative and its 1's complement form.

So convert the answer into its true form, as follows:

But

$$(0\ 1\ 0\ 1)_2 = (5)_{10}$$

$\therefore (4)_{10} - (9)_{10} = (-5)_{10}$

### **Case 3 : Both number negative:**

**Ex. 2.3 :** Perform  $(-4)_{10}$  -  $(-8)_{10}$  using 1's complement method.

Soln.:

$$(-4)_{10}$$

-  $(-8)_{10}$  =  $(-4)_{10}$  +  $(8)_{10}$

Here number A i.e.  $(-4)_{10}$  is negative and B is positive.

So we have to take the 1's complement of A.

## **Step 1 : Convert number A to 1's complements:**

$$(4)_{10} = (0100)_2$$

1's complement of  $(0100)_2 = (1011)_2$

#### **Step2**: Add 1's complement of A to number B:

1's complement of

$$(4)_{10} = 1 \quad 0 \quad 1 \quad 1$$

$$(8)_{10} = + \quad 1 \quad 0 \quad 0 \quad 0$$

Final carry  $\boxed{1} \quad 0 \quad 0 \quad 0 \quad 1$  Result

## Step2: Add the final carry 1

Answer in the true form =  $0.1 \cdot 0.0 = (4)_{10}$

Thus, the answer is positive and in the true form

$$\therefore (-4)_{10} - (-8)_{10} = (4)_{10}$$

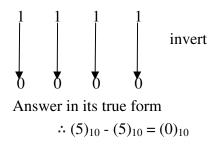

### **Case 4: Equal and opposite numbers:**

The last possibility in subtraction of numbers is to subtract a number from itself. Refer previous example to understand the result of this subtraction.

Ex. 2.4 Subtract  $(5)_{10}$  from  $(5)_{10}$  using 1's complement.

**Soln.** : We are supposed to perform  $(5)_{10}$  -  $(5)_{10}$ .

**Step 1**: Obtain 1's complement of  $(5)_{10}$ :

1's complement of  $(5)_{10}$  or  $(0\ 1\ 01)_2$  is  $(1010)_2$ .

## Step 2 : Add $(5)_{10}$ and 1's complement of $(5)_{10}$ :

## Step 3: Convert the answer to its true form:

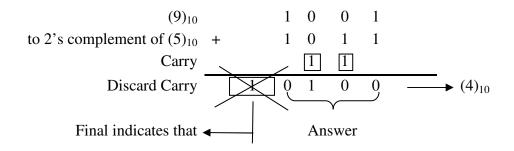

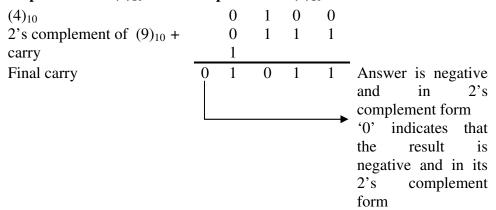

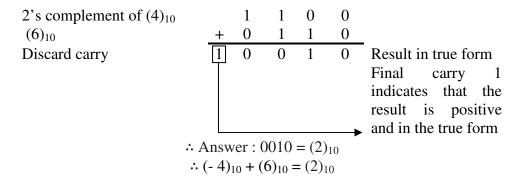

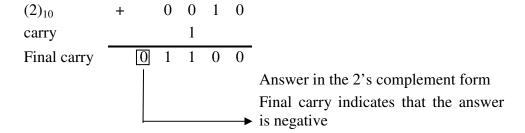

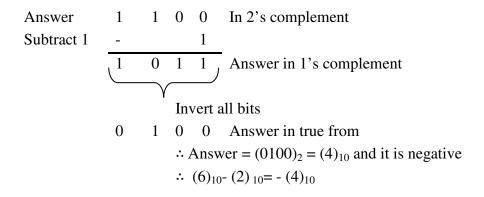

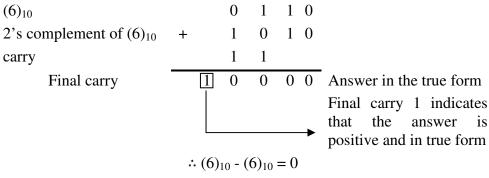

## 2.4.2 Binary Subtraction using 2's Complement Method:

If the subtraction of two binary numbers A and B is to be performed using the 2's complement, then the following steps are to be followed.

## Steps to be followed:

**Step 1**: Add  $(A)_2$  to the 2's complement of  $(B)_2$

**Step 2**: If the carry is generated then the result is positive and in its true form.

**Step3**: If the carry is not produced, then the result is negative and in its 2's complements form.

**Note:** Carry is always to be discarded in the subtraction using 2's complement.